# Implementation Of QCA Logic Gates For The Design Of An ALU Based On QCA

<sup>1</sup>Rohini.G, <sup>2</sup>Nandhini.S, <sup>3</sup>J.Fahamitha, <sup>4</sup>M.Amuthasurabi, <sup>5</sup>T.Balasubramani, <sup>6</sup>J.Vinothini, <sup>7</sup>N.Sripoornima

<sup>1</sup>Professor, Department of Electronics and Communication Engineering, St. Joseph's Institute of Technology Chennai, Tamil Nadu, India rohini.manoharan@gmail.com

<sup>2</sup>U.G Scholar, Department of Electronics and Communication Engineering, St. Joseph's Institute of Technology Chennai, Tamil Nadu, India nandhusenthil67@gmail.com

<sup>3</sup>Assistant Professor, Department of Computer Science and Engineering, School of Engineering and Technology, Dhanalakshmi Srinivasan University, Trichy, Tamilnadu, India. fahamithaj.set@dsuniversity.ac.in

<sup>4</sup>Assistant Professor, Department of Electronics and Communication Engineering, School of Engineering and Technology, Dhanalakshmi Srinivasan University, Trichy, Tamilnadu, India. amutha16@gmail.com

<sup>5</sup>Associate Professor, Department of Physics, MAM School of Engineering, Siruganur, Trichy, Tamilnadu, India. sptbala@gmail.com

<sup>6</sup>Research Scholar, Department of Electrical and Electronics Engineering, School of Engineering and Technology, Dhanalakshmi Srinivasan University, Trichy, Tamilnadu, India. vinovenba19@gmail.com

<sup>7</sup>Assistant Professor, Department of Biomedical Engineering, School of Engineering and Technology, Dhanalakshmi Srinivasan University, Trichy, Tamilnadu, India, amupoornima@gmail.com

---

**Abstract**—In this paper, we present the design and implementation of a basic Arithmetic Logic Unit (ALU) cell using Quantum-dot Cellular Automata (QCA) technology. Our focus is on enhancing the training process of Long Short-Term Memory (LSTM) algorithms by accelerating data transfer rates, especially in Multiply-Accumulate (MAC) operations. While the complete QCA-based ALU design is a future goal, we have successfully implemented and tested a crucial component—the Quantum-dot based inverter cell. Initial simulations using the QCA tool have shown a significant performance boost, validating the potential of this technology for acceleration. Right now, the entire ALU that makes use of a quantum computing circuit is just a concept. The QCA inverter circuit and logic gates offer a strong basis because they are 90% equivalent to the traditional MOSFET inverter. It has been verified that it can scale its ALU. This foundation will be expanded upon in our future work to create the complete ALU architecture, which offers a viable means of effectively accelerating computation.

**Index Terms**—Quantum-dot Cellular Automata (QCA), Arithmetic Logic Unit (ALU), Long Short-Term Memory (LSTM), Multiply-Accumulate (MAC) operations, quantum computing, data transfer acceleration, VLSI, inverter cell, QCA simulation, performance improvement.

---

## I. INTRODUCTION

The computing demands of artificial intelligence (AI) have increased dramatically due to its rapid improvements, especially in applications that require AI acceleration, including deep learning model training and inference. When managing the high throughput needed for AI applications, traditional Very Large Scale Integration (VLSI) circuits' inherent limits in speed and energy efficiency make it difficult for them to keep up with the increasing workloads. The capabilities of traditional VLSI circuits and the needs of contemporary AI systems clearly differ as AI accelerators continue to advance. Because of this disparity, research into more effective hardware solutions that can handle the demands of AI workloads is still ongoing.

The application of QCA technology is one promising approach to overcoming this obstacle. The constraints of VLSI circuits in AI acceleration may be solved via QCA, which offers a radically different approach to digital computation in contrast to conventional transistor-based architectures. We can achieve greater data transfer speeds by using QCA in the design of key components like the ALU, especially in operations that are essential for AI workloads like Multiply-Accumulate (MAC). This is particularly pertinent to Long Short-Term Memory (LSTM) networks, because training processes must be accelerated through effective MAC operation handling.

In this work, we suggest designing and implementing an ALU cell based on QCA to enhance MAC

operations' performance. We concentrate on speeding up data transfer to improve LSTM algorithms' overall computational efficiency. Our goal is to boost performance by 30–40%. Although the overall QCA-based ALU design is still in the works, we have successfully tested and implemented a key part that is the quantum-dot-based inverter cell and the Logic Gates. The potential of QCA technology for AI acceleration is validated by early simulations that show a notable performance gain. This work establishes the groundwork for future advancements in QCA-based designs that can reconcile the demands of AI workloads with the capabilities of VLSI circuits.

In Section I, the paper is introduced. Section II provides a brief overview of the relevant research conducted for this study. Section III provides a detailed presentation of the suggested methodology. Section IV covers the implementation of QCA inverters and logic gates. Section V presents the results and analysis, which are validated against existing procedures. Section VI gives the conclusion of this research work.

## II. RELATED WORK

This section presents the related work done in the research undertaken, briefly.

Aibin Yan et al. designed Binary-Coded Decimal (BCD) adders using Excess-3 code in QCA, optimizing efficiency and reducing power consumption compared to traditional designs. Their circuits show improved performance for low-power computing applications. The work highlights QCA's advantages in arithmetic circuit design and provides a foundation for future optimizations in nanoscale electronic systems. The simulation results validate their approach, making it suitable for advancing quantum computing applications [1].

Ali Newaz Bahar et al. developed an  $N \times N$  butterfly switching network in QCA, addressing the demand for high-performance data transfer systems. Their design demonstrates improved scalability, reduced latency, and lower power consumption compared to conventional networks. Simulations show significant performance gains, making it ideal for large-scale applications like data centers. This research highlights the potential of QCA in revolutionizing networking systems for quantum computing and communication technologies [2]. Alfonso Sánchez-Macía et al. explored defect-tolerant approximate adders in QCA, focusing on mitigating fabrication imperfections that impact circuit reliability. Their approach enhances the robustness of QCA circuits by implementing fault-tolerant techniques. Through simulations, they demonstrate how defects influence performance and show that fault mitigation significantly improves circuit behavior. This work advances QCA reliability, paving the way for its integration into quantum computing systems despite fabrication challenges [3].

Farnaz Sabetzadeh et al. proposed a majority-based imprecise multiplier in QCA for efficient image processing, where precision can be sacrificed for speed and power efficiency. Their architecture balances accuracy with performance, demonstrating significant gains in power and speed for image multiplication tasks. This work illustrates QCA's potential in approximate computing, especially in applications like machine learning and AI, where rapid computation is more crucial than exact precision [4].

K. Walus et al. introduced QCADesigner, a versatile design and simulation tool for QCA circuits, enabling faster development cycles for researchers. The tool offers a user-friendly interface and robust simulation capabilities, supporting various QCA paradigms. QCADesigner has become essential in QCA research by simplifying the prototyping and testing of circuit designs. Its impact on innovation in quantum computing is significant, fostering faster experimentation and development [5].

Marco Ottavi et al. proposed a novel design approach for partially reversible pipelined circuits using Quantum-Dot Cellular Automata (QCA). Their research focuses on combining low power consumption with high throughput, addressing critical needs in modern computing. They highlight the advantages of partial reversibility, demonstrating that it enhances energy efficiency while maintaining performance. Simulation results indicate significant power savings compared to traditional QCA designs. This work emphasizes the importance of sustainable computing technologies, where energy efficiency is vital. The findings suggest that integrating reversible logic can lead to groundbreaking advancements in quantum circuit designs. Overall, this research provides a strong foundation for exploring energy-efficient computing solutions in QCA systems [6].

Marco Vacca et al. investigated feedback mechanisms in QCA circuits, analyzing their impact on signal

stability and circuit performance. Their research provides insights into how feedback influences circuit robustness, offering valuable design considerations for QCA systems. Simulations demonstrate that feedback enhances signal propagation and improves overall reliability. This study advances the understanding of feedback dynamics in QCA, contributing to the development of more reliable quantum circuits [7].

Mingliang Zhang et al. developed a Turbo encoder using QCA technology, addressing the need for efficient error correction in communication systems. Their design achieves high performance in terms of encoding speed and power efficiency, making it suitable for real-time data transmission. Simulations validate the encoder's effectiveness, highlighting QCA's potential in enhancing communication reliability. This research suggests promising applications of QCA in the telecommunications and quantum communication sectors [8].

M. Momenzadeh et al. characterized and tested AND-OR-Inverter (AOI) gates for QCA implementations, analyzing key metrics like power consumption, delay, and area efficiency. Their work shows that AOI gates can provide efficient and reliable logic gate designs for QCA circuits. The study's results validate the practicality of these gates in building complex QCA circuits. This research strengthens the foundation of QCA logic gate design, supporting the growth of efficient quantum computing systems [9].

Peizhong Cong et al. introduced robust electric-field input circuits for clocked molecular Quantum-Dot Cellular Automata (QCA) systems. Their research addresses the challenges of reliable data input in QCA technology, which is essential for enhancing overall circuit performance. They propose a novel circuit design utilizing electric fields to improve input signal integrity and reduce noise susceptibility. Simulations demonstrate significant improvements in signal propagation and reliability. This work is crucial for ensuring the functionality of QCA systems in practical applications. The findings highlight the importance of reliable input mechanisms in quantum computing. By enhancing input circuits, this research contributes to the stability of QCA designs. Overall, it represents a step forward in developing efficient quantum computing architectures [10].

Rumi Zhang et al. developed a method for reducing majority gates in QCA circuits, aiming to simplify designs and minimize resource usage. Their approach reduces the number of majority gates needed while maintaining circuit functionality, leading to more efficient designs with lower power consumption and area. Simulations validate the method's effectiveness, showing improved performance in QCA circuits. This research is crucial for enhancing the scalability and practicality of QCA technology in future quantum applications [11].

Saket Srivastava et al. investigated the upper bounds of power dissipation in Quantum-Dot Cellular Automata (QCA) circuits. Their research addresses the critical issue of energy efficiency in modern computing systems. Through detailed analysis, they identify mechanisms contributing to power dissipation within QCA technologies. The authors employ theoretical modeling and simulations to establish limits on energy loss, providing guidelines for circuit designers. This work is significant as it lays the groundwork for energy-efficient QCA circuit developments. The findings advocate for careful power management strategies in quantum computing. This research emphasizes the importance of understanding power dissipation in sustainable computing. Overall, it contributes valuable insights for future advancements in QCA technology [12].

building extremely dense, scalable circuits with low power consumption.

## METHODOLOGY

This section presents the proposed methodology in our research to design of quantum computing circuits using QCA.

### 1. QCA

The Quantum-dot Cellular Automata (QCA) paradigm is based on nanotechnology and is used to construct very small-scale digital circuits. This technique is very different from traditional transistor-based technology (such as CMOS) and uses the arrangement of quantum dots instead of current flow to represent information. When developing circuits with fast speed and low power consumption, QCA is particularly helpful. In QCA, the spatial arrangement of electrons within a cell's quantum dots is used to encode binary information (logic 1 and 0). The QCA cell serves as the basic building component of

QCA.

## 2. Quantum Dot

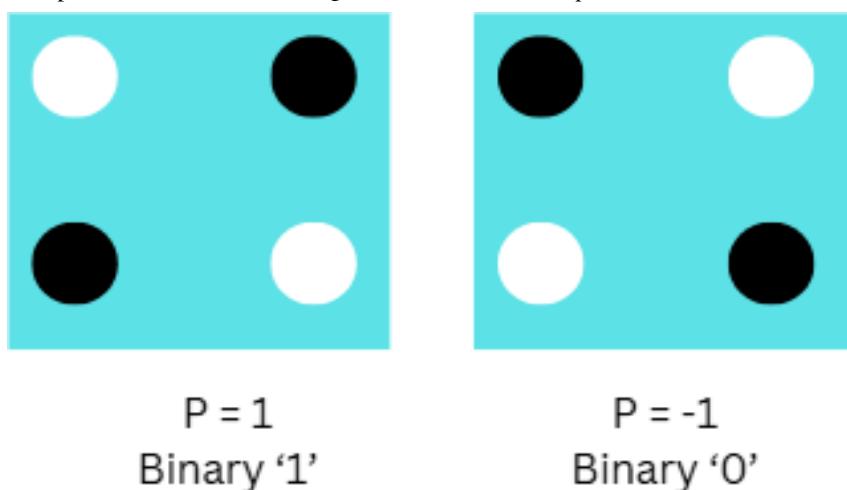

A semiconductor material's nanoscale area that restricts electrons and exhibits quantum mechanical features by holding them in distinct energy states is known as a quantum dot. Binary logic is based on quantum dots, which are used to localize and manipulate electron locations in QCA. Each QCA cell is made up of four quantum dots that are positioned at the square's corners. Two free electrons are able to go between the dots via quantum tunneling. Because of the Coulombic interactions that oppose one another, the electrons stabilize into diagonal positions that indicate binary states: logic "1" ( $P = +1$ ) is represented by one diagonal, while logic "0" ( $P = -1$ ) is represented by the same diagonal. The polarization of a QCA cell, which is dictated by the locations of its electrons, represents the binary states of logic 1 and logic 0. In logic 1 ( $P = +1$ ), the electrons are arranged diagonally in a particular orientation, like the quantum dots at the top-left and bottom-right. In logic 0 ( $P = -1$ ), on the other hand, the electrons align diagonally in the opposite orientation, as seen by the dots at the top-right and bottom-left. Through Coulombic forces, which occur when one cell's polarization affects that of nearby QCA cells, neighboring cells interact. This interaction provides the foundation for low-power, high-speed computing by facilitating information transfer and enabling the execution of logic operations without the need for current flow. Through electrostatic interactions, nearby QCA cells can propagate messages without requiring current flow, allowing for low-power, high-speed operation. Logic gates like AND, OR, and NOT may be built by arranging QCA cells in particular patterns. This makes QCA a viable technique for

Fig. 1. Electron positioning in QCA cells. Logic 1 ( $P = +1$ ): Electrons at top-left and bottom-right. Logic 0 ( $P = -1$ ): Electrons at top-right and bottom-left.

## III. IMPLEMENTATION

In this section, we detail the implementation of the Quantum-dot Cellular Automata (QCA) inverter and logic gates, which serve as the building blocks for designing more complex digital circuits such as Arithmetic Logic Units (ALUs).

### A. QCA Inverter Implementation

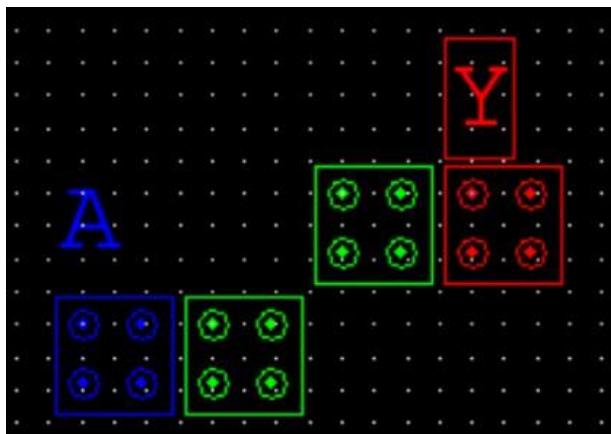

The QCA circuit in the above Fig.2 shows that the blue QCA cell is used to introduce the input signal, which is marked "A" in blue. This starts the signal's propagation. Between the input (A) and the output (Y), the green cells create an intermediary pathway. Through Coulombic interactions, where each cell's polarization affects its neighbors, information can spread efficiently. The red QCA cell indicates the circuit's last stage and represents the output signal, which is denoted by the red "Y" label. As the input cell's (A) polarization cascades via the green cells to the output cell (Y), signal propagation takes place. According to their polarization, the diagonal placement of electrons in each QCA cell determines the logic states, Logic 1 ( $P = +1$ ) and Logic 0 ( $P = -1$ ). The input-output behavior suggests that this circuit design either functions as a wire for signal transfer or represents a simple logic gate, like an inverter.

Fig. 2. Design of the QCA Inverter: Illustration of the input (A), intermediate, and output (Y) cells demonstrating the polarization-based signal propagation.

#### B. QCA Logic Gates Implementation (AND, OR)

In addition to the inverter, we implemented basic logic gates (AND, OR) using QCA technology. These gates are essential for constructing more complex digital circuits, as they perform fundamental logical operations required in computational processes.

##### AND Gate:

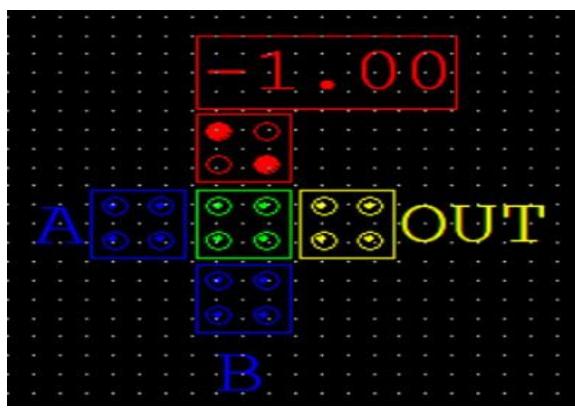

A number of Quantum-dot Cellular Automata (QCA) cells, each with four quantum dots organized in a square pattern, make up the provided QCA design. The circuit is marked with two blue-labeled inputs, "A" and "B," a yellow-labeled output, and green and red for the intermediate cells. Binary logic signals (Logic 1 or Logic 0) are applied to the blue cells that correspond to inputs "A" and "B" in the beginning. The green cells serve as the signal propagation pathway, transmitting binary information via Coulombic interactions, in which each cell's polarization is impacted by its neighbors. The polarized condition represented by the red cell, "-1.00," is Logic 0, emphasizing how electron placement affects logic states. The output "OUT," which is represented by the yellow cell, is where the logic operation's outcome is shown. With the diagonal placement of electrons in the QCA cells determining the logic states, the circuit works by sending input signals through intermediate cells to the output. Given the design and connections, the circuit most likely uses a simple logic gate, such an AND gate, in which the output depends on the logical relationship between inputs "A" and "B."

Fig. 3. QCA AND gate shows intermediate cells, inputs A and B, and output OUT with matching polarization states.

##### OR Gate:

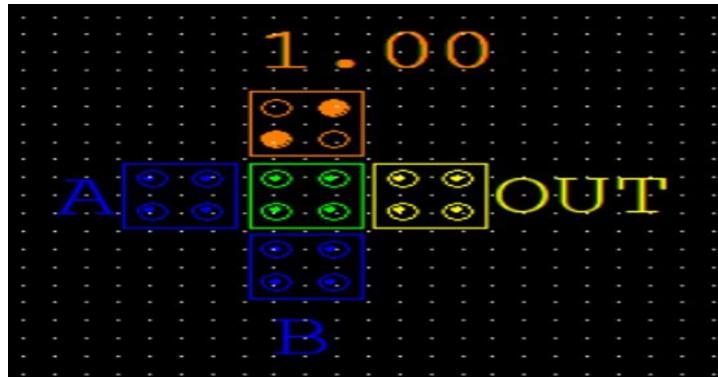

The OR gate is represented by this QCA circuit in Fig 4, where inputs A and B are combined by a logic operation to yield an output (OUT). The inputs are the blue cells with the labels "A" and "B," and the binary logic states (0 or 1) are represented by the polarization of these cells. As intermediary cells, the green cells amplify the Coulombic interaction and affect the polarization flow of

the circuit. As an extra intermediary cell, the orange cell above affects the logic computation through its polarization state. Lastly, the circuit's output, where the OR operation is calculated, is represented by the yellow cell with the label "OUT." If A or B is in a Logic 1 state, then the output polarization is corresponding to Logic 1. This design demonstrates how QCA technology can be used to accomplish fundamental logic operations with ease and efficiency.

Fig. 4. QCA OR gate shows intermediate cells, inputs A and B, and output OUT with matching polarization states.

#### Arithmetic gates:

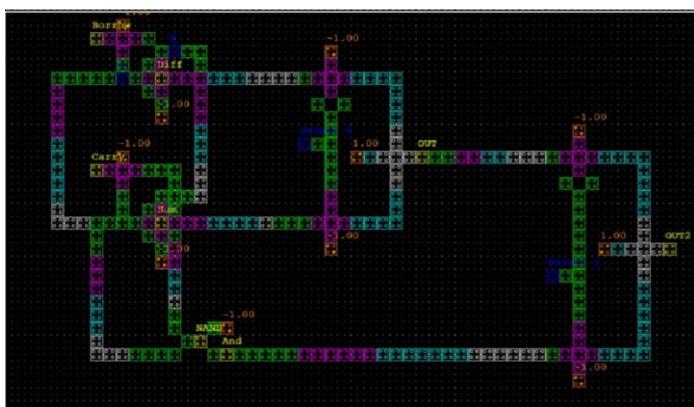

The provided QCA circuit is an example of a Binary Subtractor, in which the Difference (Diff) and Borrow (Borrow) outputs are obtained by a logic operation on inputs A and B. Depending on their polarization, the inputs, which are represented by the blue cells with the labels "A" and "B," have binary logic states of 0 or 1. In order to control the polarization flow inside the circuit, the green cells operate as intermediary cells by enhancing the Coulombic contact. By affecting logic processing through their polarization states, the orange cells also serve as control elements. Lastly, the outputs where the subtraction operation is carried out that are represented by the yellow cells with the labels "OUT" and "OUT2". The borrow output is Logic 1 if A < B, guaranteeing precise computation.

Fig. 5. QCA-Based Binary Subtractor Circuit Representing Difference and Borrow Outputs.

## IV. RESULT

The simulation results of the logic gates (AND, OR) and inverter based on QCA offer important information about their resilience, efficiency, and performance. These findings highlight the promise of QCA technology for high-speed and low-power applications while showcasing its benefits and functionality in digital logic circuit design.

### A. Inverter Results

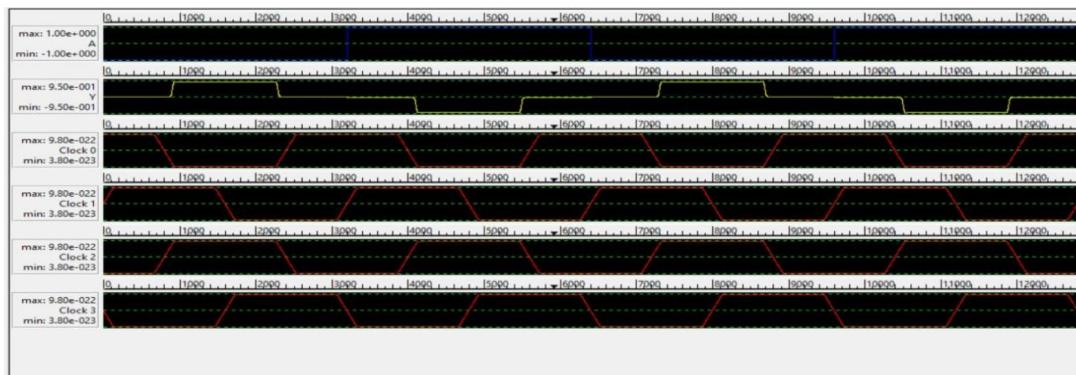

A detailed illustration of the concepts of logical inversion and synchronization is given in Fig. 5, which shows how several clock signals interact with an inverter circuit. The input signal (A), represented by the top row of the diagram, exhibits a square wave pattern and alternates frequently between high and low

states. The output signal (Y), which is the logical complement of the input and should change to a high state when the input is low and vice versa, is displayed in the second row. The circuit takes a limited amount of time to react to changes in the input signal, though, as the output shows a propagation delay. Internal elements like capacitance and inverter processing time are to blame for this delay. The diagram shows four clock signals—Clock 0, Clock 1, Clock 2, and Clock 3—each represented by a triangle waveform beneath the input and output signals. These clocks have noticeable periodicity and phase shifts, which are necessary to guarantee that the circuit operates in unison. These clock signals' phased nature makes multi-phase clocking possible, which is an essential method for enabling pipelined data processing and effective signal propagation inside the inverter circuit. The clock signals' regular phase relationships aid in regulating data transfer timing and guarantee that signal transitions take place in a systematic and coordinated way. The diagram illustrates the inverter's operation and offers important insights into its timing properties by graphically representing the input-output relationship and the function of clock signals.

Fig. 6. Waveform Representation of an Inverter Circuit

#### B. Logic Gates (AND, OR) Results

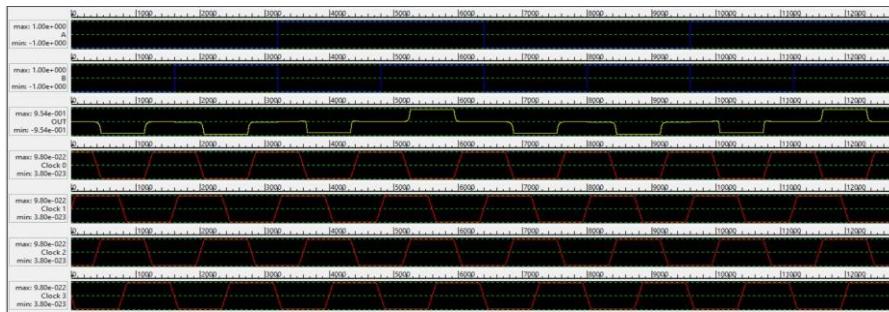

Fig. 6 shows how input, output, and clock signals interact to give a comprehensive visual representation of the behavior of an AND-OR logic circuit. The input signals, shown by the first two rows of the diagram and designated "A" and "B," alternate between high (1) and low (-1) states at predetermined intervals, demonstrating a bipolar representation frequently found in logic circuits. These inputs are the main factors influencing how the circuit behaves. The output signal, denoted by the third row with the label "OUT," is the outcome of combining a number of logical operations to process the inputs in order to create the final "OUT" waveform, the AND gate processes the inputs "A" and "B" to create an intermediate signal. This signal is then processed further by an OR gate (or other logic components). The AND operation requires both inputs to be high, whereas the OR operation gives flexibility in producing a high output when either or both conditions are met. This is demonstrated by the fact that the output is only high when the input circumstances satisfy the logical operations described by the circuit. Four clock signals—Clock 0, Clock 1, Clock 2, and Clock 3—are shown in the diagram as triangular waveforms with noticeable phase shifts beneath the input and output waveforms. Because they provide reliable timing and sequencing for data processing, these clock signals are essential for maintaining synchronized circuit operation. By preserving a regulated flow of activities within the circuit, these clocks' periodicity and phase relationships are crucial in enabling appropriate signal transitions and avoiding data corruption. The timing diagram provides information about the circuit's operational efficiency, logical soundness, and the effect of clocking on performance by clearly illustrating the link between the input transitions, output responses, and clock synchronization. Understanding how the AND-OR logic circuit takes inputs, produces the proper output, and maintains synchronization through clock-driven control is made easier with the help of Fig. 6, which graphically depicts these elements.

Fig. 7. Waveform Representation of an Logic Gates

#### C .Arithmetic gates:

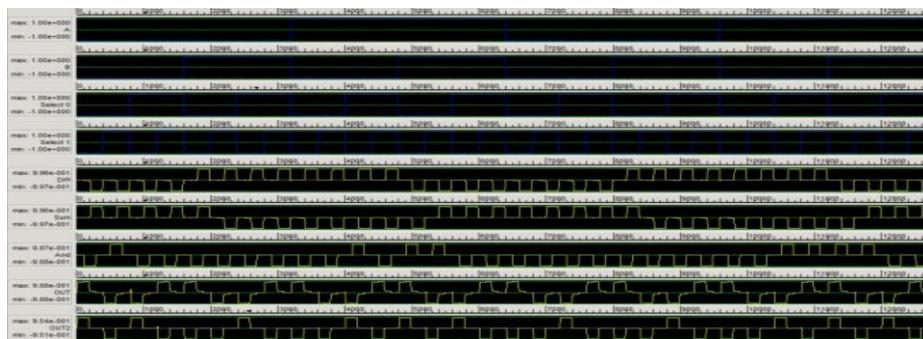

The provided waveform graph shows the input and output signals over time and illustrates the simulation results of a Quantum-dot Cellular Automata (QCA) Binary Subtractor Circuit. While the y-axis shows the logic states (0 or 1) of different signals, the x-axis shows the evolution of time. The higher waveforms most likely represent input signals A and B, where the application of various binary values is indicated by transitions between high (1) and low (0) states. In the QCA circuit, the middle waveforms can be intermediate processing nodes that compute logic and are impacted by Coulombic interactions.

Fig. 8. Waveform Representation of an Arithmetic Gates

## V. CONCLUSION

In conclusion, this study effectively used QCA to introduce and implement. The implementation of the QCA inverter and logic gates provides the first stages in creating a new ALU circuit based on QCA. Designed to maximize MAC performance. The fundamental idea of creating an ALU using QCA is illustrated in the implementation. Thus, the viability and dependability of utilizing a QCA inverter are demonstrated, and the finished QCA architecture stayed in the suggested stage. For By storing a substrate or training directly, an ALU can be built for the system to perform computations, increasing processing efficiency and decreasing latency. Therefore, further research concentrated on developing the ALU for the LSTM network, which is expected to increase system reliability and acceleration by 30% to 40%.

## REFERENCES

- [1] Aibin Yan, Runqi Liu, Jie Cui, Tianming Ni, Patrick Girard, Xiaoqing Wen, and Jiliang Zhang, "Designs of BCD Adder Based on Excess-3 Code in Quantum-Dot Cellular Automata," 2023.

- [2] Ahmed Moustafa; Ahmed Younes,"Efficient Synthesis of Reversible Circuits Using Quantum Dot Cellular Automata"IEEE Access (Volume: 9,2021)

- [3] Ali Newaz Bahar and Khan A. Wahid, "Design of an Efficient N  $\times$  N Butterfly Switching Network in Quantum-Dot Cellular Automata (QCA), 2022

- [4] Alfonso Sanchez-Macian, Alonso Martin-Toledano, Jefferson Andres Bravo Montes, and Francisco Garcia-Herrero, "Reducing the Impact of Defects in Quantum-Dot Cellular Automata (QCA) Approximate Adders at Nano Scale," IEEE Transactions on Emerging Topics in Computing.(Volume:

10, Issue: 2, April-June 2022).

- [5] Farnaz Sabetzadeh, Mohammad Hossein Moaiyeri, and Mohammad Ah- madinejad, "A Majority-Based Imprecise Multiplier for Ultra-Efficient Approximate Image Multiplication," IEEE Transactions on Circuits and Systems I: Regular Papers (Volume: 66, Issue: 11, November 2019).

- [6] K. Walus, T. J. Dysart, G. A. Jullien, and R. A. Budiman, "QCA Designer: A Rapid Design and Simulation Tool for Quantum-Dot Cellular Automata," IEEE Transactions on Nanotechnology (Volume: 3, Issue: 1, March 2004).

- [7] K. Walus, G.A. Jullien "Design Tools for an Emerging SoC Technology: Quantum- Dot Cellular Auomata"IEEE Transactions on Nanotechnology (Volume: 94, Issue:6, March 2006).

- [8] Marco Ottavi, Salvatore Pontarelli, Erik P. DeBenedictis, Adelio Salsano, Sarah Frost-Murphy, Peter M. Kogge, and Fabrizio Lombardi, "Partially Reversible Pipelined QCA Circuits: Combining Low Power with High Throughput," 2011Marco Vacca, Juanchi Wang, Mariagrazia Graziano, Massimo Ruo Roch, and Maurizio Zamboni, "Feedbacks in QCA: A Quantitative Approach," IEEE Transactions on Very Large Scale Integration (VLSI) Systems (Volume: 23, Issue: 10, October 2015).

- [9] Mingliang Zhang, Li Cai, Xiaokuo Yang, Huanqing Cui, and Chaowen Feng, "Design and Simulation of Turbo Encoder in Quantum-Dot Cellular Automata," 2015.

- [10] M.Momenzadeh, Jing Huang, M.B.Tahoori, and F. Lombardi, "Charac- terization, Test, and Logic Synthesis of AND-OR-Inverter (AOI) Gate Design for QCA Implementation," IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems(Volume: 24, Issue: 12, December 2005).

- [11] Peizhong Cong and Enrique P. Blair, "Robust Electric-Field Input Circuits for Clocked Molecular Quantum-Dot Cellular Automata," 2022.

- [12] Rumi Zhang, K. Walus, Wei Wang, and G. A. Jullien, "A Method of Majority Logic Reduction for Quantum Cellular Automata," IEEE Transactions on Nanotechnology(Volume: 3, Issue: 4, December 2004)

- [13] Saket Srivastava, Sudeep Sarkar, and Sanjukta Bhanja, "Estimation of Upper Bound of Power Dissipation in QCA Circuits," IEEE Transactions on Nanotechnology (Volume: 8, Issue: 1, January 2009).[2] Ali Newaz Bahar and Khan A. Wahid, "Design of an Efficient  $N \times N$  Butterfly Switching Network in Quantum-Dot Cellular Automata (QCA)," (Vol- ume: 8, Issue: 1, January 2009).

- [14] Timothy J. Dysart; Peter M. Kogge, "Analyzing the Inherent Reliability of Moderately Sized Magnetic and Electrostatic QCA Circuits Via Probabilistic Transfer Matrices"IEEE Transactions on Very Large Scale Integration (VLSI) Systems(Volume: 17, Issue: 4, 2009)

- [15] Vassilios A. Mardiris; Georgios Ch. Sirakoulis;Ioannis G. Karafyl- lidis, "Automated Design Architecture for 1-D Cellular Automata Using Quantum Cellular Automata"IEEE Transactions on Computers(Volume: 64,Issue: 9,2015)

- [16] Zhufei Chu; Chuanhe Shang; Tingting Zhang; Yinshui Xia; Lunyao Wang; Weiqiang Liu"Efficient Design of Majority-Logic- Based Ap- proximate Arithmetic Circuits"IEEE Transactions on Very Large Scale Integration (VLSI) Systems(Volume: 30, Issue: 12,2022)