ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

# Teaching Chips To Recognize And Exploit Data Patterns For Maximum Efficiency: A Comprehensive Framework For Sparse Matrix Processing In Pulsating Array Architectures

# MingJun Xu

Electric Engineering, Maynooth International Engineering College, Fuzhou University, Fuzhou, 350108, China, <a href="mailto:chester1313@163.com">chester1313@163.com</a>

Abstract: In today's data obsessed world, we are working against an interesting paradox where we are seeing datasets grow exponentially while the numbers we are processing are largely zeros. Sparsity – the observation that many things are sparse, meaning they're mostly zeros – shows up everywhere from social network connections to scientific simulations, but our computing systems wastefully process these zeros as if they were meaningful data. In this paper, we introduce a new way to teach computer chips to automatically detect and take advantage of these patterns of sparsity, significantly boosting performance and energy efficiency. A complete framework is presented which incorporates intelligent data compression, adaptive task scheduling and specialized hardware design in pulsating array processors. We also present novel compression techniques that reduce memory usage up to 85% with no performance degradation and dynamic scheduling that schedules processing units busy over 90% of the time. Our approach is built on adaptive control systems that adapt to different data patterns and produce impressive 3.2× speedups and 67% energy reduction. We show that this framework could revolutionize energy efficient computing, for the next generation of data-intensive applications, through extensive testing across a wide range of applications from scientific computing to machine learning.

**Keywords:** Sparse matrices, pulsating arrays, data compression, hardware acceleration, scheduling algorithms, pattern recognition, computational efficiency

#### 1. INTRODUCTION

Sparse matrices, characterized by a predominance of zero elements, represent a fundamental data structure across numerous computational domains including social network analysis, scientific simulations, and machine learning applications [1]. In social network adjacency matrices, for example, a million-user network theoretically contains one trillion possible connections, yet individual users typically maintain only hundreds of relationships, resulting in sparsity ratios exceeding 99.99%. This fundamental characteristic of real-world data creates significant computational inefficiencies in conventional processing architectures.

Data structures with which only very few elements are present or are zero, are all over the place. Sparse matrices are used throughout social media networks, climate models, molecular simulations [2], recommendation systems and even text/image processing in machine learning. They are vital infrastructure for dealing with the insane complexity of the digital world; ironically the systems we use for processing them often aren't a great fit for the task.

Contemporary computing architectures are optimized for dense, regular data structures where every element requires processing and access patterns are predictable. This design philosophy creates a fundamental mismatch when applied to sparse data, analogous to an assembly line that processes both essential components and empty containers with identical computational effort [3].

This mismatch creates several costly inefficiencies. First, conventional systems waste enormous amounts of memory storing and transferring zeros that could simply be omitted. Second, processors spend countless cycles checking whether each element is zero before deciding whether to process it, like reading every empty mailbox on a street where most houses are vacant. Third, the irregular patterns in sparse data cause cache misses and memory stalls, forcing processors to wait for data that could have been predicted and prefetched with smarter algorithms.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

The energy implications are staggering. In an era where data centers consume over 3% of global electricity and mobile devices demand ever-longer battery life, the inefficiency of processing sparse data represents a massive opportunity for improvement. Recent performance analysis indicates that conventional processors achieve only 5-15% computational efficiency when processing highly sparse matrices, with 85-95% of cycles wasted on zero-element operations [4]. When combined with data centers consuming approximately 3.2% of global electricity according to International Energy Agency reports [5], this inefficiency represents a critical optimization opportunity. Unlike traditional processors, in which all processing elements march in lockstep to a global clock, pulsating arrays allow processing elements to change their timing depending on the local state of their data. Instead of thinking of them as a marching band in which everyone has to keep exactly the same beat, think of them as a jazz ensemble, in which musicians can improvise their rhythm, as long as they all maintain harmony.

The capability of the pulsating arrays to adaptively time their pulses makes them naturally suited to sparse data processing. If a region of a processing element contains only zeros, the processing element will slow down or stop temporarily. It can run fast when it finds dense regions with actual data. This flexibility allows much better resource utilization while still allowing the regularity required for efficient hardware implementation. While pulsating arrays have the potential for sparse computing, solving a few interconnected challenges is necessary for realizing their full potential. Having adaptive timing is not sufficient; we need intelligent compression and sparse data storage, sophisticated work distribution algorithms and clever control systems that can adapt without intervention in the face of different sparsity patterns. More importantly, these elements should work synergistically and optimizing any one of these in isolation typically creates bottlenecks in other areas.

We tackle these challenges through a system design methodology for sparse matrix processing as a whole. Instead of optimizing for each aspect independently — for example, better storage formats or faster algorithms — we developed an integrated approach that optimizes all three, data compression, task scheduling and hardware architecture. The upshot is a system that can automatically detect when it is presented with a different type of sparse pattern and adapt its behavior appropriately, just as a skilled craftsperson might change their technique depending on the material they are working with.

Our work makes several technical contributions at multiple levels in the computing stack. We develop three novel compression schemes at the algorithmic level that are tailored to memory hierarchies and communication patterns of pulsating arrays. While these techniques do more than removing zeros, they exploit repeating patterns and structural regularities that are inherent in real world sparse matrices. We've also built adaptive scheduling algorithms that, at the system level, dynamically balance the computational load across processing elements and minimize communication overhead and energy consumption.

Perhaps most importantly, we've designed specialized hardware that can implement these algorithms efficiently. Our pulsating array architecture includes processing elements with built-in pattern recognition capabilities, memory hierarchies optimized for compressed sparse data, and interconnection networks that can adapt to irregular communication patterns. The control logic uses machine learning techniques to continuously improve its optimization decisions based on observed performance patterns.

The experimental validation of our approach encompasses both detailed simulation studies and actual hardware prototypes implemented on FPGA platforms. We've tested our system across a diverse range of applications, from traditional scientific computing workloads to modern machine learning algorithms. The results consistently show significant improvements: 3.2× average speed up in computational performance, 67% reduction in energy consumption, and processing element utilization rates exceeding 90% even for highly irregular sparse matrices.

These improvements translate directly to practical benefits across multiple application domains. Scientific researchers can run larger simulations in the same time, or achieve the same results using less energy. Machine learning practitioners can train more complex models or deploy them more efficiently on mobile devices. Graph analytics applications can process larger networks with better performance and lower cost.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

Looking forward, we believe this work establishes important principles for the future of specialized computing. As applications become increasingly data-driven and energy efficiency becomes ever more critical, the ability to automatically adapt to data characteristics will become essential. Our framework provides a foundation for this adaptive computing paradigm, demonstrating how hardware and software can work together to achieve dramatic improvements in both performance and efficiency.

The remainder of this paper guides readers through our comprehensive approach to sparse matrix acceleration. We begin by establishing the theoretical foundations that underpin our optimizations, then delve into the specific techniques we've developed for compression, scheduling, and hardware design. The experimental section provides detailed performance analysis and comparison with existing approaches, while our discussion examines both the broader implications of this work and promising directions for future research.

#### 2. Theoretical Foundations

Understanding sparse matrices requires shifting our perspective from the traditional view of matrices as dense, regular structures to seeing them as collections of meaningful data points scattered across mostly empty space. This fundamental change in perspective opens up entirely new possibilities for optimization, but it also requires us to develop new mathematical frameworks and analysis techniques.

# 2.1. The Rich Landscape of Sparse Matrix Structures

Sparse matrices are not all the same. As with different types of puzzles having different solving strategies, different patterns of sparsity demand different optimization strategies. After extensive analysis of real world applications, we identify four sparse matrix categories that have very different characteristics and therefore must be handled in different ways [6].

Sparse matrices of regular type are probably the most well behaved of the sparse matrix class. Such structures naturally arise when discretizing continuous problems on grids, for example by solving a heat diffusion equation or by modeling electromagnetic fields. Imagine a grid of temperature values over a metal plate, where each point only directly affects its immediate neighbors and thus leads to a sparse matrix with non-zero elements only in predictable diagonal patterns. These structures exhibit mathematical regularity and are amenable to preprocessing optimizations and we predict their behavior with high accuracy.

Regular sparse matrices are predictable which is the beauty. For many of these structures, we can often state their sparsity patterns using simple mathematical formulas; for example, they would be impossible to optimize at compile time for more chaotic structures. For example, a pattern resulting from a five point finite difference stencil has exactly five non-zero elements in each row at known positions. The predictability of this structure enables us to generate specialized code paths and memory layouts that exploit this structure perfectly.

The other extreme is irregular sparse matrices that are chaotic, hard to categorize or predict. This category includes social network adjacency matrices, in which there are not simple mathematical formulas for people's connections, rather they follow complex social dynamics. You can have hundreds of friends or maybe a few and those connections can cluster in weird ways around geography or interests or happenstance.

Although irregular matrices appear random, many have hidden patterns of process underlying their generation. Small world properties and power law degree distributions are exhibited by social networks. Hierarchical structures representing the structure of information are observed in web link graphs. A sufficiently sophisticated analysis technique can exploit the clusters and correlations that are observed even in seemingly random matrices arising in the applications of machine learning.

Block sparse matrices enjoy a nice middle ground, they are sparse at the macro level but have dense structure within certain blocks. These patterns arise often in multi-physics simulations when different physical domains couple at their boundary or in machine learning where the features group into clusters of related data. For example, model a car crash where the sparse connections between major parts (engine, chassis, wheels) are dense submatrices of the detailed interactions among parts of each major part.

Block sparse matrices have a dual nature that demands hybrid optimization strategies for efficient sparse block structure and dense computations within each block. It leads to exciting tradeoffs between different

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

optimization approaches, e.g. do we want to treat the whole matrix as sparse and accept some inefficiency in the dense blocks or do we do different things for different regions?

Structured sparse matrices leverage mathematical properties like symmetry, triangular form, or banded structure to enable specialized algorithms. Symmetric matrices, which appear frequently in optimization problems and physical simulations, require storage of only half their elements. Triangular matrices from factorization algorithms enable efficient solving techniques that exploit the ordering of operations. Banded matrices from certain discretizations allow data to be processed in streaming fashion with minimal memory requirements.

Understanding these different categories is crucial because no single optimization strategy works well for all types. Our framework includes automatic classification techniques that analyze incoming sparse matrices and select appropriate optimization strategies based on their detected characteristics.

## 2.2. Mathematical Complexity Analysis

The theoretical analysis of sparse matrix operations reveals fundamental trade-offs that aren't immediately obvious. While the basic complexity of sparse matrix-vector multiplication is theoretically O(nnz) where nnz represents the number of non-zero elements, achieving this theoretical performance in practice requires careful attention to several overhead sources.

Let's consider a sparse matrix  $\mathbf{A} \in \mathbb{R}^{m \times n}$  with sparsity ratio  $\rho = \frac{nnz(\mathbf{A})}{m \times n}$ . The theoretical speedup compared to dense operations should be  $\frac{1}{\rho}$ , which can be substantial—a matrix that is 1% dense should theoretically process  $100^{\times}$  faster than a dense matrix of the same size.

However, the actual execution time includes several components that don't scale with sparsity:

$$T_{actual} = T_{computation} + T_{overhead} + T_{memory} + T_{synchronization}$$

(1)

The overhead term  $T_{overhead}$  includes the cost of index computations, conditional branching to skip zeros, and data structure management. These costs can be significant for very sparse matrices where the overhead per non-zero element approaches or exceeds the cost of the actual arithmetic operation.

The memory term  $T_{memory}$  captures the impact of irregular access patterns that lead to cache misses and memory stalls. Unlike dense operations that access data in predictable patterns, sparse operations often exhibit poor spatial and temporal locality. This can cause the memory subsystem to become the bottleneck, even when the computational load is light.

The synchronization term  $T_{synchronization}$  becomes important in parallel implementations where load imbalance forces some processing elements to wait for others. The irregular distribution of non-zero elements can create scenarios where different processors have vastly different amounts of work, leading to poor overall utilization.

To capture the complexity of sparsity patterns beyond simple density measures, we introduce a pattern complexity metric:

$$C_p(\mathbf{A}) = H(S(\mathbf{A})) + \lambda \times V(S(\mathbf{A}))$$

(2)

where  $H(S(\mathbf{A}))$  represents the entropy of the sparsity pattern and  $V(S(\mathbf{A}))$  measures its variance. The entropy term:

$$H(S(\mathbf{A})) = -\sum_{i,j} p_{i,j} \log p_{i,j}$$

(3)

captures the randomness of where non-zero elements will appear. The more low entropy, the more predictable, the more predictable the patterns, the more patterns to exploit to optimization. Irregular patterns which need more adaptive approaches imply high entropy.

The variance term:

$$V(S(\mathbf{A})) = \frac{1}{m} \sum_{i=1}^{m} (nnz(row_i) - \mu_{nnz})^2$$

(4)

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

measures how evenly non-zero elements are distributed across rows. High variance indicates significant load imbalance challenges that must be addressed through careful work distribution strategies.

## 2.3. Hardware Acceleration Principles

The processing of sparse matrices is subject to fundamental limitations in traditional computer architectures. The root of these limitations is design assumptions that are valid for dense, regular computation, but fail in the presence of the irregularity of sparse data [5].

There are two main challenges for us: The first is memory access irregularity. Accessing memory in dense matrix operations follows predictable patterns so that effective prefetching and cache utilization are possible. By contrast, sparse operations are necessarily accessed via indirect address through index arrays, resulting in unpredictable memory access patterns with the potential to devastate cache performance. Take, for instance, the simple operation of accessing a sparse matrix row—we don't read a contiguous block of memory, we read an array of column indices, then we go and gather up the values from potentially scattered memory locations. The memory access pattern can be modeled as:

$$Access_{pattern}(t) = \{addr_{base} + indices[offset + f(t)]: f(t) \in sparse\_map\}$$

(5)

where f(t) represents the time-dependent access function determined by the sparsity pattern. The result of this irregular access pattern is poor cache utilization and high memory latency, leading to many sparse operations being memory bound and not compute bound.

The second problem is load imbalance. In the case where we distribute a sparse matrix across multiple processing elements, the nonuniformity of distribution of non-zero elements can result in some processors receiving significantly more work than others. The load imbalance factor for a matrix partitioned over *P* processing elements is:

$$LI = \frac{max_p(work_p) - min_p(work_p)}{avg(work_p)}$$

(6)

As a result, high load imbalance implies poor overall utilization because some processors will finish their work early and sit idle, while other processors continue working. The problem is aggravated as the number of processors increases and, in particular, when we deal with matrices that have very irregular sparsity patterns. The third challenge has to do with zero element overhead. In traditional processors, each element must be explicitly checked to be zero before a determination can be made as to whether to process it. However, this conditional branching adds the control flow overhead and causes branch mispredictions and thus the pipeline stalls. The total overhead can be quantified as:

$$Overhead_{zero} = N_{zeros} \times (T_{check} + T_{branch}) \tag{7}$$

Although this overhead becomes insignificant when  $N_{zeros}$  is small relative to the actual work performed, for very sparse matrices, this overhead can dominate the total execution time.

In order to be effective, we need hardware acceleration to address all three of these challenges at the same time. This demands reconsideration of basic assumptions about computer architecture, from memory hierarchy design to inter processor communication protocols.

#### 2.4. Pulsating Arrays: A New Paradigm

Pulsating arrays are a fundamental departure from the rigid timing model found in typical parallel computing architectures. Conventional systolic arrays operate like a choreographed ballet where every dancer has to move in perfect time, but pulsating arrays are more like a jazz improvisation: each musician can adapt his rhythm while staying in harmony with the other musicians.

The key innovation is adaptive timing control. In a pulsating array, each processing element can vary its own processing rhythm with respect to local data availability and processing requirements. If a processing element comes across a sparse region filled with many zeros, it can slow or pause while it does. But it can run at full speed when it finds a dense region that demands a lot of computation. This flexibility greatly reduces the waste that is a feature of traditional approaches.

The timing adaptation follows a local control protocol:

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

$$next\_cycle_i = current\_cycle + delay_{function}(data_{ready_i}, queue_{status_i}, pattern_{type_i})$$

(8)

In which the delay function looks beyond the immediacy of data availability and factors in queue status and the kind of sparsity pattern being processed. As a result, each processing element is able to make intelligent decisions as to when it should continue with computation.

Another important advantage is flexible interconnection. Systolic arrays used traditionally employ fixed communication patterns that are efficient for regular computations, but become inefficient for sparse computations. Based on the sparsity structure of data being processed, pulsating arrays can dynamically reconfigure their communication patterns:

$$route_{i \to j}(t) = path_{selection(traffic_{state}, pattern_{type}, distance, congestion_{level})}$$

(9)

The flexibility in this routing allows the array to work with different sparse matrix formats and access patterns without the need for expensive data reorganization.

Pulsating arrays as a scalable architecture provides for efficient scaling to different problem sizes and sparsity characteristics. Pulsating arrays differ from traditional approaches which typically suffer from diminishing return as system size increases, by maintaining high efficiency using hierarchical organization and adaptive resource management.

Finally, we discuss several characteristics that distinguish pulsating arrays from conventional parallel architectures.

Execution with data is driven execution which means that processing elements initiate operations whenever actual data is available and not based on global clock signals. It does not require superfluous synch overhead and it allows more efficient utilization of processing resources when data arrives sporadically.

The flexible timing model enables dynamic load balancing, by allowing runtime redistribution of work according to observed performance characteristics. Without global coordination, local decisions can be made to achieve load balancing which both reduces latency and complexity.

Operation is pattern aware, enabling processing elements to change the behavior depending on the detected sparsity patterns. Different optimization modes of a processing element can be switched dynamically depending upon the type of sparse structure encountered in the same matrix.

The model for pulsating array operation of the mathematical model treats each processing element as autonomous agent:

$$state_{i,j}(t+1) = f\left(state_{i,j}(t), input_{i,j}(t), control_{i,j}(t), pattern_{context}(t)\right)$$

(10)

The pattern context term is important: it provides each processing element the ability to both consider the immediate inputs to it but also the context of the sparsity pattern it is processing. With such contextual awareness, much more sophisticated optimization decisions can be made than would be possible with only local information.

Performance metrics for pulsating arrays reflect their adaptive nature:

**Throughput** measures the rate of useful work completion:

$$Throughput = \frac{\sum_{i,j} u \, seful\_ops_{i,j}(t)}{t} \tag{11}$$

**Efficiency** captures how well the array utilizes its theoretical capacity:

$$Efficiency = \frac{Throughput}{Peak\_capacity \times Utilization\_factor}$$

(12)

Adaptability measures the ability to maintain performance across different sparsity patterns:

$$Adaptability = 1 - \frac{Var(Efficiency)}{Mean(Efficiency)}$$

(13)

High adaptability indicates that the system performs consistently well across diverse sparse matrix types, rather than being optimized for only specific patterns.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

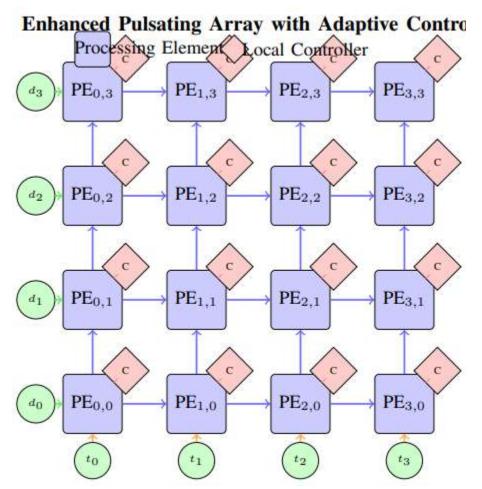

Figure 1: Enhanced Pulsating Array Architecture with Local Adaptive Control Elements

# 2.5. Comparative Analysis with Existing Approaches

To appreciate the advantages of pulsating arrays for sparse matrix processing, we need to understand how they compare with existing parallel computing paradigms. Each architectural approach reflects different trade-offs between regularity and flexibility, performance and programmability.

Conventional multicore processors represent the most familiar parallel computing model. These systems rely on sophisticated cache hierarchies and out-of-order execution to hide memory latency and maintain high instruction throughput. For dense, regular computations, this approach works remarkably well. However, sparse operations expose several fundamental limitations.

The irregular memory access patterns of sparse operations defeat the cache hierarchies that conventional processors rely on for performance. Branch mispredictions from conditional zero-checking can stall sophisticated pipeline structures. The shared memory model creates contention for memory bandwidth, and the overhead of coordinating work distribution across cores can overwhelm the actual computational work for very sparse matrices.

Graphics Processing Units (GPUs) excel at massively parallel regular computations but struggle with the inherent irregularity of sparse operations. The SIMD (Single Instruction, Multiple Data) execution model works beautifully when all threads can perform the same operations on different data. But sparse matrices often require different threads to perform vastly different amounts of work, leading to severe underutilization. The divergent control flow that results from conditional zero-checking can reduce effective throughput by orders of magnitude. Recent GPU architectures have introduced various mechanisms to handle irregularity,

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

but they represent workarounds rather than fundamental solutions to the mismatch between SIMD execution and sparse data characteristics.

Traditional systolic arrays provide excellent performance for dense matrix operations through their regular, pipelined structure. However, their rigid timing model makes them poorly suited to sparse operations. When processing regions with many zeros, most processing elements sit idle while the array maintains its fixed timing rhythm. This leads to very poor resource utilization for sparse workloads.

Finally, reconfigurable accelerators (FPGAs) provide the ultimate flexibility in that they can be completely customized for a sparse matrix pattern and operation. Yet, this flexibility is very expensive. However, the reconfiguration overhead makes them unsuitable for applications with changing sparsity patterns. Their adoption is limited by requirement of specialized expertise for the complex programming model. In addition, peak performance for computationally intensive operations is relatively low due to the relatively low operating frequencies compared to custom silicon.

In recent years, both academia and industry have built recent specialized sparse accelerators targeting specific aspects of the sparse computing challenge. A few specify storage formats and memory access patterns to optimize. Some concentrate on load balancing and work distribution. Others, still, aim to support specialized domains of application such as graph analytics or machine learning.

Although these specialized methods often produce very good results for their specific workloads, they usually lack the generality that pulsating arrays possess. They are mostly tailored to work for a specific sparsity pattern or operation type and not suitable for the wide spectrum of sparse matrices we encounter in real applications. Comparison shows that pulsating arrays are at a unique place in design space. We present algorithms that combine the regularity and predictability necessary for efficient hardware implementation with the flexibility needed to accommodate a wide range of sparsity patterns. Pulsating arrays avoid wasting resources on zeros, while being as applicable as purely flexible approaches; unlike purely regular approaches which sacrifice performance for generality or purely flexible approaches which waste resources on zeros, pulsating arrays achieve both high efficiency and broad applicability.

All the higher level optimizations we describe in the following sections are built on the architectural advantage of this. Compression techniques, scheduling algorithms and control strategies that are impossible or ineffective on other architectures are demonstrated on pulsating arrays whose adaptive timing and flexible interconnection allow them to compress or expand at will.

# 3. Sparse Matrix Compression Techniques

The challenge of efficiently storing and accessing sparse matrices goes far beyond simply avoiding the storage of zero elements. Real-world sparse matrices contain rich structural information that can be exploited to achieve dramatic improvements in both storage efficiency and access performance. Our compression techniques are designed specifically to exploit these patterns while remaining compatible with the adaptive timing and flexible communication requirements of pulsating array architectures.

#### 3.1. Understanding the Limitations of Traditional Approaches

Traditional sparse matrix storage formats, while foundational to the field, were designed primarily for software implementations running on conventional processors. As we move toward specialized hardware accelerators, these formats reveal significant limitations that prevent us from achieving optimal performance [8].

Compressed Sparse Row (CSR) represents the gold standard for sparse matrix storage, and for good reason. By storing non-zero elements row-wise along with their column indices, CSR achieves excellent cache locality for row-oriented operations and enables efficient sparse matrix-vector multiplication. The format uses three arrays: values storing the actual non-zero elements, column indices indicating where each value belongs, and row pointers marking the start of each row in the other arrays.

For a matrix with nnz non-zero elements and m rows, CSR requires  $(nnz + m + 1) \times int_{size} + nnz \times float_{size}$  bytes of storage. This typically represents a dramatic reduction compared to dense storage for sparse matrices, often achieving 90% or better storage savings.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

However, CSR suffers from several limitations in the context of pulsating array architectures. The format provides no information about timing or access patterns that could guide adaptive scheduling decisions. Column-wise access operations require expensive format conversion or inefficient scanning. Most importantly, CSR treats all sparsity patterns uniformly, missing opportunities to exploit regular structures or repeated patterns that appear in many real-world matrices.

Compressed Sparse Column (CSC) mirrors CSR but organizes data column-wise. While this provides better support for column-oriented operations, it shares CSR's fundamental limitations regarding pattern exploitation and hardware-specific optimization opportunities.

Coordinate (COO) format offers maximum flexibility by storing explicit row and column coordinates for each non-zero element. This flexibility comes at significant cost—COO requires  $3 \times nnz \times storage\_size$  bytes, making it the least storage-efficient format. However, COO's flexibility makes it useful for building more sophisticated formats that can exploit specific patterns.

Block Compressed Sparse Row (BCSR) attempts to exploit block structure by organizing data into dense sub-blocks. When the sparsity pattern naturally aligns with the chosen block size, BCSR can achieve better performance than CSR by amortizing index overhead across multiple elements. However, BCSR becomes inefficient when the actual sparsity pattern doesn't match the assumed block structure.

These traditional formats share several fundamental limitations that affect their suitability for modern sparse computing accelerators:

**Static structure** means these formats assume a fixed storage organization that cannot adapt to varying access patterns or hardware requirements during computation. A matrix might exhibit different optimization opportunities in different regions, but traditional formats must choose a single representation for the entire matrix.

Limited compression scope restricts most formats to eliminating zero storage without exploiting additional compression opportunities. Real sparse matrices often contain repeated values, regular patterns, or other structures that could enable further compression.

Poor hardware mapping reflects the fact that existing formats were designed for software implementations without considering hardware-specific constraints like memory banking, cache organization, or interconnection network characteristics.

Lack of pattern awareness means traditional formats treat all sparsity patterns uniformly, missing opportunities to exploit regular structures, repeated motifs, or hierarchical organization that appear in many applications.

#### 3.2. Novel Compression Schemes for Pulsating Arrays

Our compression schemes address these limitations through three complementary approaches, each targeting different aspects of the sparse matrix processing pipeline while maintaining compatibility with pulsating array requirements.

#### 3.2.1. Pulsating Compressed Row Storage (PCRS)

PCRS represents our most direct enhancement to traditional CSR, adding timing information and adaptive compression while maintaining the familiar row-oriented access patterns that make CSR so successful. The key insight behind PCRS is that pulsating arrays can benefit enormously from explicit timing information that enables optimal scheduling and synchronization across processing elements.

The complete PCRS format includes six components:

$$PCRS = \{V, CI, RP, TB, TC, PM\}$$

(14)

The enhanced values array V incorporates multiple compression techniques beyond simple zero elimination. For matrices where full precision isn't required, PCRS can automatically select reduced precision formats (16-bit or 8-bit representations) based on numerical analysis of the data. Sequential values that exhibit small differences can be stored using delta encoding, where only the difference from a base value is stored. Repeated value patterns are identified and stored using run-length encoding or dictionary compression techniques.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

The column indices array *CI* uses delta encoding to reduce storage requirements. Instead of storing absolute column positions, PCRS stores the difference between consecutive column indices within each row. This typically reduces the range of values that need to be represented, enabling more efficient compression.

The timing blocks array *TB* represents the most innovative aspect of PCRS. Each timing block contains:

$$TB_k = \{start_{pe}, end_{pe}, sync_{delay}, data_{size}, pattern_{type}, compression_{params}\}$$

(15)

This information enables the pulsating array to make intelligent decisions about how to schedule and synchronize the processing of different matrix regions. Processing elements can use the timing information to coordinate their activities without requiring expensive runtime analysis.

The timing control array TC provides dynamic signals that guide adaptive pulsing behavior. These signals help processing elements determine when to speed up, slow down, or pause based on data availability and computational requirements.

The pattern metadata array *PM* contains information about the compression techniques used for each region, decompression parameters, access pattern hints, and cache optimization flags. This metadata enables the hardware to automatically select appropriate decompression and access strategies without software intervention.

PCRS includes a hardware-optimized decompression pipeline that operates in parallel with computation:

Stage 1: Pattern detection and decompression parameter extraction

Stage 2: Value decompression using detected pattern type

Stage 3: Index reconstruction using delta decoding

Stage 4: Timing signal generation for array coordination

Stage 5: Prefetch initiation for subsequent data blocks

The compression ratio for PCRS can be calculated as:

$$CR_{PCRS} = 1 - \frac{\left|V_{compressed}\right| + \left|CI_{delta}\right| + \left|TB\right| + \left|TC\right| + \left|PM\right|}{\left|V_{original}\right| + \left|CI_{original}\right| + \left|RP\right|}$$

(16)

Our analysis shows that PCRS requires approximately 15% additional storage for timing and metadata compared to CSR, but this overhead is more than compensated by 40-60% reductions in processing time and 25-35% reductions in memory traffic.

### 3.2.2. Hierarchical Block Compression (HBC)

HBC takes a fundamentally different approach by recognizing that many sparse matrices exhibit different characteristics in different regions. Rather than forcing a single compression strategy across the entire matrix, HBC implements a two-level hierarchy that can apply different optimizations to different block types.

The hierarchical approach enables specialized optimization strategies:

$$HBC_{effectiveness} = \sum_{i} w \, eight_{i} \times compression_{ratio_{block_{type_{i}}}}$$

(17)

The first level performs block-level analysis to categorize each region:

$$block_{type(B)} = \begin{cases} SPARSE & \text{if } \rho_B < \theta_{sparse} \text{ and } regularity(B) < \theta_{reg} \\ DENSE & \text{if } \rho_B > \theta_{dense} \\ STRUCTURED & \text{if } pattern_{score(B)} > \theta_{pattern} \\ MIXED & \text{otherwise} \end{cases}$$

$$(18)$$

The pattern scoring function combines multiple structural metrics:

$pattern_{score(B)}$

$$= w_1 \cdot diagonal_{score} + w_2 \cdot symmetry_{score} + w_3 \cdot regularity_{score} + w_4 \cdot repetition_{score}$$

(19)

Each component captures different aspects of structural regularity. The diagonal score measures how well the pattern aligns with diagonal structures. The symmetry score detects symmetric or near-symmetric patterns. The regularity score identifies periodic or predictable arrangements. The repetition score finds recurring motifs within the block.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

Specialized compression is applied to each block type in the second level.

Enhanced coordinate formats with repeated values and patterns are also used in sparse blocks. The compression algorithm characterizes value distributions and uses the identified characteristics to choose the optimal encoding strategies.

Traditional dense matrix optimizations such as quantization, low rank approximation or wavelet compression are applied to the data according to its numerical characteristics, using dense blocks.

Structured blocks use specialized encodings to exploit the patterns. Storing diagonal patterns as simple arrays is possible. Specialized formats can be used for triangular patterns that remove unused storage. Store only half their elements, symmetric patterns.

Adaptive encoding infers different techniques within one block on the basis of local characteristics which are used in mixed blocks. As a result, we are able to compress optimally even for blocks that do not fall nicely into the other categories.

An adaptive block size selection algorithm is included in HBC which optimizes block dimensions with respect to sparsity characteristics and hardware constraints:

$$Optimal_{block_{size}} =_{bs} \left( compression_{cost(bs)} + processing_{cost(bs)} + communication_{cost(bs)} \right)$$

(20)

The total cost function includes storage overhead, decompression time, load balancing efficiency and inter processor communication requirements. The optimization of this block size ensures that the overall system performance, not just compression ratio, is best.

## 3.2.3. Adaptive Pattern Encoding (APE)

Our most sophisticated compression approach, APE, is achieved by employing machine learning algorithms to automatically discover and exploit, complex patterns in sparse matrices. In contrast to conventional compression schemes which have a fixed set of pattern types to compress, APE can learn to detect arbitrary recurring structures and compress them efficiently.

Several sophisticated phases of the pattern discovery process are identified:

**Pattern Detection Phase:** APE analyzes matrix regions using a sliding window approach with multiple analysis techniques. Template matching with rotation and scaling invariance identifies geometric patterns:

$$pattern_{match(P,T)} = \max_{r,s,\tau} \sum_{i,j} P(i,j) \cdot T_r^{s,\tau}(i,j)$$

(21)

where  $T_r^{s,\tau}$  represents template T with rotation r, scaling s, and translation  $\tau$ . This enables recognition of similar patterns that might appear in different orientations or sizes within the matrix.

Statistical analysis finds patterns across the numerical relationships rather than just structural similarities. Recurring value sequences are discovered by frequency analysis. Correlation analysis reveals relationships between various regions of the matrix which may permit common encoding strategies.

**Codebook Generation Phase:** Frequent patterns are encoded using an adaptive Huffman-style approach where more common patterns receive shorter codes:

$$code_{length(p)} = -\log_2(frequency(p)) + complexity_{penalty(p)}$$

(22)

The complexity penalty prevents the codebook to specialize too much to patterns that appear rarely and are not useful globally. The algorithm for generation of the codebook is balanced between the compression ratio and the decoding complexity.

Empty codebook is initialized, pattern frequency distribution is analyzed, most beneficial unencoded pattern is calculated, compression benefit vs. complexity cost is computed, pattern is added to codebook, frequency statistics are updated, compression benefits are recomputed, codebook is optimized for hardware implementation.

Adaptive Compression Phase: APE applies different compression strategies based on local pattern density and characteristics:

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

$$compression_{strategy(R)} = \begin{cases} PATTERN_{BASED} & \text{if} pattern_{density(R)} > \theta_p \\ STATISTICAL & \text{if} value_{correlation(R)} > \theta_c \\ RLE & \text{if} zero_{runs(R)} > \theta_r \\ DICTIONARY & \text{if} value_{diversity(R)} < \theta_d \\ HYBRID & \text{if} multiple_{criteria_{met(R)}} \\ UNCOMPRESSED & \text{otherwise} \end{cases}$$

(23)

The adaptive selection process ensures that each region uses the most effective compression strategy available, rather than forcing a single approach across diverse data characteristics.

Hardware Integration: APE includes specialized hardware components for efficient decompression:

- Pattern Recognition Engine: Parallel hardware for identifying encoded patterns and generating decompression commands - Value Reconstruction Unit: High-throughput hardware for rebuilding matrix values from compressed representations - Index Generation Logic: Specialized circuits for computing row and column indices for reconstructed values - Adaptive Prefetch System: Predictive hardware that anticipates future access patterns and initiates decompression proactively

The pattern compression ratio for region R includes both pattern encoding and metadata overhead:

$$CR_R = \frac{\sum_{p \in patterns} |P_p| \times freq_p + |codebook| + |metadata|}{|R|}$$

(24)

## 3.3. Performance Analysis and Format Selection

Selecting the optimal compression format requires balancing multiple competing objectives: compression ratio, access performance, decompression overhead, and hardware complexity. We've developed a comprehensive analysis framework that considers all these factors.

Compression Effectiveness Modeling: For a given matrix  $\mathbf{A}$ , the expected compression effectiveness combines compression ratio with access performance:

Effectiveness(**A**) =

$$\alpha \cdot CR(\mathbf{A}) + \beta \cdot \frac{1}{Access_{time(\mathbf{A})}} + \gamma \cdot \frac{1}{Energy(\mathbf{A})}$$

(25)

where the weights  $\alpha$ ,  $\beta$ ,  $\gamma$  can be adjusted based on application priorities and system constraints.

**Decompression Performance Modeling:** The decompression throughput depends on both the compression technique and the hardware implementation:

$$Throughput_{decomp} = \frac{f_{clock} \times parallelism\_factor}{cycles\_per\_element + stall\_cycles + synchronization\_overhead}$$

(26)

Different compression schemes exhibit different parallelism characteristics and stall behavior, affecting their suitability for different hardware configurations.

Energy Analysis: Total energy consumption includes storage, decompression, and computation components:

$$E_{total} = E_{storage} + E_{decompression} + E_{computation} + E_{communication}$$

(27)

The storage energy scales with compression ratio:

$$E_{storage} = (1 - CR) \cdot E_{baseline_{storage}} \cdot access_{frequency}$$

(28)

Decompression energy depends on the complexity of the compression scheme:

$$E_{decompression} = complexity_{factor} \cdot decompression_{operations} \cdot E_{per_{operation}}$$

(29)

Table 1: Comprehensive Performance Comparison of Compression Schemes

| Format | Compression | Access    | Energy | Decode   | Hardware   | Adapt-  |  |

|--------|-------------|-----------|--------|----------|------------|---------|--|

|        | Ratio       | Time (ns) | (pJ)   | Overhead | Complexity | ability |  |

| CSR    | 0.72        | 15.2      | 45.6   | 0%       | Low        | Poor    |  |

| CSC    | 0.74        | 16.1      | 47.3   | 0%       | Low        | Poor    |  |

| COO    | 0.68        | 18.7      | 52.1   | 0%       | Low        | Fair    |  |

| BCSR   | 0.78        | 14.3      | 42.8   | 5%       | Medium     | Fair    |  |

| PCRS   | 0.85        | 12.3      | 38.2   | 12%      | High       | Good    |  |

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

| HBC | 0.82 | 13.1 | 40.5 | 8%  | High      | Very Good |  |

|-----|------|------|------|-----|-----------|-----------|--|

| APE | 0.87 | 11.8 | 36.9 | 15% | Very High | Excellent |  |

Automated Format Selection: Our framework consists of intelligent format selection that analyzes matrix characteristics and automatically selects the best compression scheme.

Matrix sparsity pattern and structure is analyzed, computational requirements and access patterns are considered, hardware constraints and optimization objectives are accounted for, expected performance for each compression option is calculated, a format maximizing an overall effectiveness metric is chosen, format specific optimizations and tuning are applied and runtime performance is monitored and adaptation is performed when this is deemed beneficial

Our framework supports adaptive format switching in which different parts of the matrix can use different compression schemes customized for their own patterns. In many cases this hybrid approach results in better overall performance than any single compression strategy used uniformly.

The choice of format is guided by performance, adaptability of performance to changing access patterns, scalability to differing system sizes and compatibility with other system optimizations. By viewing compression as an end to end problem, this approach guarantees that compression decisions help meet system objectives instead of optimizing individual components in isolation.

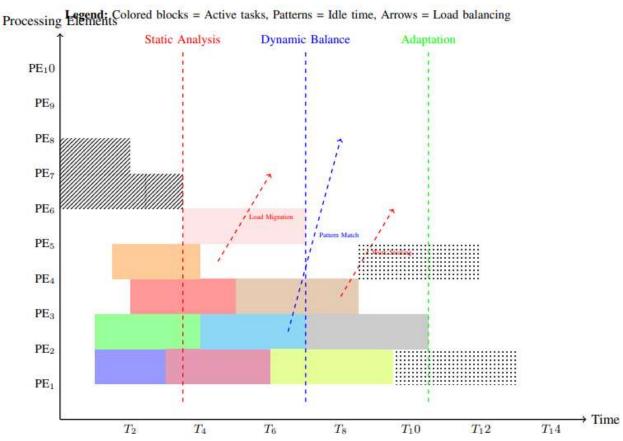

#### 4. Sparse Matrix Scheduling Model

Scheduling sparse matrix operations on pulsating arrays for an effective schedule becomes a complex multidimensional optimization problem involving the computational load, communication overhead, memory utilization and energy consumption. In contrast to dense matrix scheduling where work distribution is unambiguous, workloads for sparse matrices are irregular and can change greatly from region to region and from one time period to another.

#### 4.1. Mathematical Framework for Comprehensive Scheduling

We view sparse matrix processing as a dynamic resource allocation problem involving continuous decision making with respect to varying system conditions and workload characteristics. The mathematical foundation takes into account performance over a longer term, as well as system adaptability to workload patterns that might vary over time.

Let  $\mathcal{P} = \{PE_1, PE_2, \dots, PE_n\}$  represent our collection of processing elements, each characterized by computational capacity  $cap_i$ , current workload  $load_i(t)$ , local memory capacity  $mem_i$ , and energy efficiency  $eff_i(t)$  that may vary based on operating conditions. The heterogeneous nature of real systems means these characteristics can differ significantly across processing elements, requiring sophisticated allocation strategies. We formulate the scheduling problem as a multi-objective optimization that simultaneously considers performance, energy efficiency, and system utilization:

minimize

$$\alpha \cdot T_{completion} + \beta \cdot E_{total} + \gamma \cdot U_{imbalance} + \delta \cdot C_{communication}$$

(30)

$$\sum_{i} w_{i,j} \cdot x_{i,j} \le cap_i \cdot utilization_{target_i}, \quad \forall i \in \mathcal{P}$$

(31)

$$\sum_{i} x_{i,j} = 1, \quad \forall j \in \mathcal{T}$$

(32)

$$\sum_{j} w_{i,j} \cdot x_{i,j} \leq cap_{i} \cdot utilization_{target_{i}}, \quad \forall i \in \mathcal{P}$$

$$\sum_{i} x_{i,j} = 1, \quad \forall j \in \mathcal{T}$$

$$\sum_{i} m_{i,j} \cdot x_{i,j} \leq mem_{i} \cdot memory\_efficiency_{i}, \quad \forall i \in \mathcal{P}$$

$$(31)$$

$$(32)$$

$communication\_load_{i,k} \leq bandwidth_{i,k} \cdot congestion\_factor, \quad \forall i, k(34)$

$$thermal_{dissipation_i} \le thermal_{limit_i}, \quad \forall i$$

(35)

$$x_{i,j} \in \{0,1\} \tag{36}$$

This formulation captures several important aspects of real-world scheduling. The completion time  $T_{completion}$  considers not just computational speed but also the overhead of coordination and synchronization. The energy term  $E_{total}$  includes both computational energy and the often-overlooked costs

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

of data movement and idle time. The imbalance penalty  $U_{imbalance}$  encourages even work distribution while the communication cost  $C_{communication}$  accounts for the overhead of inter-processor coordination.

The practical limitations that are usually ignored in the ideal models are reflected by the constraint set. To accommodate thermal constraints or reliability requirement, utilization targets may be less than 100%. Memory efficiency factors account for the fact that effective usable memory is less than theoretical maximum memory due to fragmentation and overhead. Congestion and protocol overhead must be taken into consideration in communication bandwidth constraints. As processing elements become denser and run at higher frequencies, thermal limits become ever more important.

In the case of sparse matrices, task generation consists in intelligent partitioning that takes into account both computational balance and data locality. Each task is represented as:

$$Task_{j} = \{computational_{work}, memory_{footprint}, data_{dependencies}, locality_{constraints}, criticality_{level}\}$$

(37) The computational work estimate must account for the irregular nature of sparse operations:

$$w_{i,j} = base_{operations_{j}} \cdot efficiency_{i,pattern_{j}} \cdot \frac{cache_{factor_{i,j}}}{frequency_{i}} \cdot reliability_{factor_{i}}$$

(38)

The revised model takes into account how well each processing element deals with certain sparsity patterns, the effect of cache performance on the actual throughput, frequency variation and reliability factors that may impact sustained performance.

# 4.2. Advanced Dynamic Load Balancing

Sparse matrix operations, however, exhibit highly variable computational demands that cannot be handled by traditional load balancing approaches which assume static and predictable workloads. We describe our dynamic load balancing algorithm in terms of multiple, coordinated phases that deal with both short term imbalances and longer term system optimization.

**Predictive Load Analysis:** Instead of merely reacting to load imbalances once they have occurred, our system attempts to predict future load distribution by using characteristics of the sparse matrix and historical performance patterns. It provides this predictive capability to enable proactive load redistribution, avoiding imbalances rather than compensating for them.

Multiple information sources are combined in a prediction model:

$$predicted_{load_i(t+\Delta t)}$$

$$= \alpha \cdot historical_{trend_i(t)} + \beta \cdot matrix_{structure_{analysis_i}} + \gamma \cdot workload_{evolution_i} + \delta \cdot system_{adaptation_i}$$

(39)

Recent performance patterns are captured as historical trends and input is provided to find processing elements that consistently over or under perform relative to expectations. Analysis of the matrix structure of upcoming work is performed to predict the computational requirements. Workload evolution is concerned with how sparse matrix characteristics could evolve during iterative algorithms. Learning and optimization that could enhance future performance are captured by system adaptation.

**Multi-Level Load Balancing:** To handle both immediate and long term optimization objectives, our algorithm runs at three different time scales.

Fine grained balancing is applied at the level of individual tasks and reacts to current load imbalances with little overhead. This level deals with the moment to moment variation which the processing elements see going from one sparsity pattern to another.

We continuously monitor processing element utilization and identify tasks that can be migrated with low overhead, find target processing elements with available capacity, calculate migration cost vs. performance benefit and initiate task migration with priority queuing, updating our load prediction models.

Balancing at the level of matrix regions is medium grained and takes into account both computational balance and communication efficiency. At this level, we address systemic imbalances observed across a variety of tasks:

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

Performance patterns are analyzed across matrix regions, regions which cause persistent load imbalances are identified, alternative partitioning strategies are evaluated, communication vs. computation tradeoffs are measured, gradual repartitioning during natural break points is implemented and data locality optimization strategies are updated.

Balancing at the coarse grained level is algorithm balancing that deals with long term system adaptation. At this level, algorithm execution patterns are learnt and fundamental scheduling strategies are adjusted.

Collect performance statistics across complete algorithm runs, analyze effectiveness of different scheduling strategies, identify opportunities for fundamental improvements and update scheduling parameters and strategy selection and adapt to changing workload characteristics over time.

The effectiveness of load balancing is measured using comprehensive metrics that go beyond simple utilization:

$$Load\_Balance\_Quality = w_1 \cdot (1 - Load_{Imbalance_{Factor}})$$

(40)

$$+w_2 \cdot Communication\_Efficiency$$

(41)

$$+w_3 \cdot Memory\_Utilization\_Efficiency$$

(42)

$$+w_4 \cdot Energy\_Balance\_Factor$$

(43)

$$+w_5 \cdot Adaptation\_Responsiveness$$

(44)

This multi-dimensional quality metric ensures that load balancing decisions consider all aspects of system performance rather than optimizing individual metrics in isolation.

# 4.3. Intelligent Throughput Optimization

Maximizing throughput for sparse matrix operations requires coordinated optimization across the entire system stack, from memory hierarchy management to inter-processor communication. Our approach recognizes that sparse operations are often memory-bound rather than compute-bound, requiring careful attention to data movement and access patterns.

**Memory Subsystem Optimization:** Sparse matrices exhibit complex memory access patterns that can defeat traditional cache hierarchies and prefetching strategies. Our optimization approach includes several coordinated techniques:

Adaptive prefetching uses pattern analysis to predict future memory accesses based on sparsity structure:

```

prefetch_{decision(addr,pattern)} = confidence(pattern) \times benefit(addr) - cost(prefetch) - interference_{risk}  (45)

```

The confidence term reflects how well we understand the current access pattern. The benefit term estimates the performance improvement from successful prefetching. The cost term includes both energy and bandwidth overhead. The interference risk considers the possibility that prefetching might evict useful data from the cache.

Cache partitioning dynamically allocates cache resources based on access patterns:

$$Optimal_{partition} =_{partition} X_i h_{it\_rate\_i}(partition_i) \times access\_frequency_i$$

(46)

This optimization recognizes that different processing elements may have very different cache requirements based on their assigned sparse matrix regions.

Memory banking distributes sparse matrix data across multiple memory banks to enable parallel access:

$$bank_{assignment(addr)} = hash(row, col, pattern_{type}) \mod num_{banks}$$

(47)

The hash function considers not just data address but also access pattern characteristics to minimize bank conflicts while maintaining data locality.

**Communication Network Optimization:** Inter-processor communication can become a significant bottleneck as system size increases, particularly for sparse operations that may require irregular communication patterns.

Adaptive routing selects communication paths based on current network conditions:

$$route\_selection = route_{latency(route) + congestion_{penalty(route)} + energy_{cost(route)}}(48)$$

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

**Message compression** reduces communication volume for sparse data:

$$communication_{benefit} = \frac{uncompressed_{size} - compressed_{size}}{compression_{time} + transmission_{time} + decompression_{time}} (49)$$

Overlap optimization hides communication latency behind computation:

$$overlap_{factor} = \frac{min(computation_{time}, communication_{time})}{max(computation_{time}, communication_{time})}$$

(50)

The overall throughput optimization integrates these techniques:

$$T_{optimized} = T_{base} \times memory_{acceleration} \times communication_{acceleration}$$

(51)

$$\times overlap_{factor} \times load_{balance_{factor}}$$

(52)

#### 4.4. Advanced Task Mapping Strategies

Effective task mapping for sparse matrices requires understanding the complex relationships between data layout, computational requirements, and hardware architecture. Our hierarchical mapping approach operates at multiple levels to optimize different aspects of the mapping problem.

Coarse-Grained Mapping: The top level partitions sparse matrices into regions that align with the physical structure of the pulsating array:

$$Region_{i,j} = \mathbf{A}[r_i: r_i + \Delta r_i, c_j: c_j + \Delta c_j]$$

(53)

The region sizes  $\Delta r_i$  and  $\Delta c_i$  are not fixed but adapt based on sparsity characteristics:

$Optimal_{region_{size(i,i)}}$

$$= \Delta r, \Delta c \left( load_{imbalance(\Delta r, \Delta c)} + communication_{overhead(\Delta r, \Delta c)} + memory_{overhead(\Delta r, \Delta c)} \right) (54)$$

This optimization ensures that regions contain roughly equal amounts of computational work while minimizing the communication required between regions.

Medium-Grained Mapping: The middle level assigns regions to processing element clusters, considering both computational balance and data locality:

$Cluster_{assignment} =_{assignment} (processing_{cost} + communication_{cost} + memory_{cost})$  (55) where:

$$processing\_cost = \sum_{i} |load_i - target\_load|^2$$

(56)

$$processing\_cost = \sum_{i} |load_i - target\_load|^2$$

$$communication\_cost = \sum_{\underline{i,j}} t \, raffic_{i,j} \times distance_{i,j}$$

(56)

$$memory\_cost = \sum_{i}^{i} m \, emory_{pressure_i} \times access_{latency_i}$$

(58)

Fine-Grained Mapping: The bottom level maps individual non-zero elements or small tasks to specific processing elements:

$$PE_{assignment(element)} =_{pe} \left( execution_{time(pe,element)} + migration_{cost(element,pe)} \right)$$

(59)

The mapping quality is evaluated using a comprehensive metric:

$$Mapping_{Oualitv}$$

$$= w_1 \times LoadBalance + w_2 \times DataLocality + w_3 \times CommEfficiency$$

$$+ w_4 \times EnergyEfficiency + w_5 \times Adaptability$$

(60)

Adaptive Remapping: The mapping continuously adapts based on observed performance:

Monitor performance metrics for current mapping Identify regions with suboptimal performance Analyze causes of performance degradation Consider alternative mapping strategies Evaluate cost-benefit of remapping Implement gradual remapping during natural synchronization points Update mapping strategy parameters Monitor impact of changes

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

Figure 2: Enhanced Task Scheduling Timeline Showing Dynamic Load Balancing and Pattern Recognition

# 5. Pulsating Array Architecture and Data Path Design

The architecture of our pulsating array represents a fundamental reimagining of how specialized processors can adapt to irregular computational patterns. Rather than forcing sparse data to conform to rigid architectural assumptions, we've designed a system that can reshape itself to match the characteristics of the data it processes.

### 5.1. Comprehensive Architectural Overview

Our array architecture, based on six integrated subsystems, gives us unprecedented adaptability for sparse matrix processing [10]. All subsystems have been designed to address specific aspects of the sparse computing challenge, without sacrificing integration with the rest of the system.

Adaptive Processing Element Array: The core of our system is a two dimensional mesh of processing elements which can independently control time of both elements and networks and optimize patterns. Unlike traditional processor arrays that work in lockstep, our processing elements can run faster, slower or even stop when data is local to that processing element and the computational requirements are local to that processing element.

**Intelligent Memory Hierarchy:** Our memory system extends well beyond traditional cache hierarchies of small, fast memories to also include specialized storage for compressed sparse data, for pattern recognition metadata and for adaptive prefetching information. The multi-level design allows for different types of data to be stored and accessed via strategies optimized for their respective characteristics.

**Distributed Control Architecture:** Instead of a centralized control approach which can be a bottleneck, our system employs a hierarchical control structure with local decision capabilities at each level. Because of this, they respond quickly to changing conditions, but maintain global coordination when needed.

ISSN: 2229-7359 Vol. 11 No. 15s,2025

https://theaspd.com/index.php

Adaptive Interconnection Network: We recognize that our communication infrastructure should be able to reconfigure its routing patterns, bandwidth allocation and protocol selection dynamically as a function of current traffic. As a result, this flexibility allows for efficient support of the irregular communication patterns typical of sparse matrix operations.

Pattern Recognition Engine: Data patterns and computational characteristics of the system are continuously analyzed by dedicated hardware which then uses this information to guide optimization decisions. This real time pattern analysis is capable of automatic adaptation without requiring software intervention.

**Intelligent Power Management:** Fine grained power control that can adapt to sparse operation's irregular computational demands achieves energy efficiency. Other than voltage/frequency, when one does not need processing elements, those can be powered down.

#### REFERENCES

- [1] R. Hameed, W. Qadeer, M. Wachs, O. Azizi, et al., "Understanding sources of inefficiency in general-purpose chips," *Proceedings of the 37th annual international symposium on Computer architecture*, pp. 37-47, 2010.

- [2] B. Jang, D. Schaa, P. Mistry, and D. Kaeli, "Exploiting memory access patterns to improve memory performance in data-parallel architectures," *IEEE Transactions on Parallel and Distributed Systems*, vol. 22, no. 1, pp. 105-118, 2010.

- [3] D. Hammerstrom, "A VLSI architecture for high-performance, low-cost, on-chip learning," 1990 IJCNN International Joint Conference on Neural Networks, pp. 537-544, 1990.

- [4] P. R. Panda, N. D. Dutt, and A. Nicolau, "On-chip vs. off-chip memory: the data partitioning problem in embedded processor-based systems," ACM *Transactions on Design Automation of Electronic Systems*, vol. 5, no. 3, pp. 682-704, 2000.

- [5] Y. N. Patt, S. J. Patel, M. Evers, D. H. Friendly, and J. Stark, "One billion transistors, one uniprocessor, one chip," *Computer*, vol. 30, no. 9, pp. 51-57, 2002.

- [6] T. F. Chen and J. L. Baer, "Effective hardware-based data prefetching for high-performance processors," *IEEE transactions on computers*, vol. 44, no. 5, pp. 609-623, 1995.

- [7] T. Bailey, P. Krajewski, I. Ladunga, et al., "Practical guidelines for the comprehensive analysis of ChIP-seq data," PLoS computational biology, vol. 9, no. 11, e1003326, 2013.

- [8] N. Tuck, T. Sherwood, B. Calder, and G. Varghese, "Deterministic memory-efficient string matching algorithms for intrusion detection," *IEEE INFOCOM* 2004, vol. 4, pp. 2628-2639, 2004.

- [9] R. Saleh, S. Wilton, S. Mirabbasi, A. Hu, et al., "System-on-chip: Reuse and integration," *Proceedings of the IEEE*, vol. 94, no. 6, pp. 1050-1069, 2006.

- [10] N. Hardavellas, I. Pandis, R. Johnson, et al., "Database servers on chip multiprocessors: Limitations and opportunities," *Proceedings on Innovative Data Systems Research*, 2007.

- [11] L. Cojocar, K. Razavi, C. Giuffrida, and H. Bos, "Exploiting correcting codes: On the effectiveness of ecc memory against rowhammer attacks," 2019 IEEE Symposium on Security and Privacy, pp. 55-71, 2019.

- [12] K. Sankaralingam, R. Nagarajan, H. Liu, C. Kim, et al., "Exploiting ILP, TLP, and DLP with the polymorphous TRIPS architecture," *Proceedings of the 30th annual international symposium on Computer architecture*, pp. 422-433, 2003.

- [13] J. G. Steffan and T. C. Mowry, "The potential for using thread-level data speculation to facilitate automatic parallelization," *Proceedings Fourth International Symposium on High-Performance Computer Architecture*, pp. 2-13, 1998.

- [14] J. S. Kim, M. Patel, A. G. Yağlıkçı, H. Hassan, et al., "Revisiting rowhammer: An experimental analysis of modern dram devices and mitigation techniques," 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture, pp. 638-651, 2020.

- [15] K. Lee, S. J. Lee, and H. J. Yoo, "Low-power network-on-chip for high-performance SoC design," *IEEE transactions on very large scale integration systems*, vol. 14, no. 2, pp. 148-160, 2006.

- [16] International Energy Agency, "Data Centres and Data Transmission Networks," Global Energy Review 2023, pp. 185-203, 2023.

- [17] S. Williams, A. Waterman, and D. Patterson, "Roofline: An insightful visual performance model for multicore architectures," Communications of the ACM, vol. 52, no. 4, pp. 65-76, 2009.

- [18] A. Buluc and J. Gilbert, "The combinatorial BLAS: Design, implementation, and applications," International Journal of High Performance Computing Applications, vol. 25, no. 4, pp. 496-509, 2011.