ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

# Performance Evaluation of SHE-PWM using a Novel Algorithm and SPWM in Cascaded Seven-Level H-Bridge Inverter for Grid-connected Systems

Sarika Anasane<sup>1\*</sup>, Ritesh Tirole<sup>1</sup>, Amrit Ghosh<sup>1</sup> and Anand Bhaskar<sup>1</sup>

<sup>1</sup>Sir Padampat Singhania University, Rajasthan, India sarika.kuhikar@spsu.ac.in, ritesh.tirole@spsu.ac.in

Corresponding author: Sarika Anasane, Sir Padampat Singhania University, Rajasthan, India.

Email id: sarika.kuhikar@spsu.ac.in

Abstract: This paper presents a performance evaluation of Selective Harmonic Elimination Pulse Width Modulation (SHE-PWM) using a novel algorithm and Sinusoidal Pulse Width Modulation (SPWM) in cascaded seven-level H-bridge inverter in grid-connected systems. A novel optimization algorithm is introduced to compute optimal switching angles for the selective harmonic elimination method, effectively reducing total harmonic distortion across a range of modulation indices. The algorithm efficiently resolves the nonlinear transcendental equations that link switching angles, harmonic distortion, and the amplitude of the fundamental waveform. Extensive simulations conducted using MATLAB/Simulink on a resistive-inductive load (45  $\Omega$ , 0.025 H) over modulation indices from 0.7 to 1.0 reveal that the selective harmonic elimination using a novel algorithm outperforms the sinusoidal pulse width modulation method in minimizing total harmonic distortion. Specifically, at a modulation index of one, selective harmonic elimination achieves a total harmonic distortion of 11.68% compared to 17.94% for the sinusoidal pulse width modulation approach. Furthermore, the proposed algorithm successfully eliminates targeted lower order harmonics while preserving the desired fundamental voltage component, and the lower switching frequency associated with selective harmonic elimination results in reduced switching losses. These findings underscore the potential of optimized selective harmonic elimination for high-power applications where efficiency and waveform quality are important.

**Keywords:** Cascaded Seven-Level H-Bridge Inverter; Selective Harmonic Elimination PWM; Sinusoidal PWM; Total Harmonic Distortion; Modulation Index

## INTRODUCTION

The advances in power electronics have led to substantial improvement in inverter technology [1], specifically in the design of multilevel inverters for medium-voltage and high-power applications [2]. Among these, Cascaded H-bridge (CHB) multilevel inverters have received eminence due to their adaptability and better performance [3]. These inverters aid the important function of converting DC input voltage to symmetrical AC output voltage with desired frequency and magnitude [4].

While ideal inverters should produce purely sinusoidal waveforms, pragmatic operations mostly result in non-sinusoidal output waveform which contains harmonics [5]. This becomes predominantly significant in high-power applications where minimum distortion in sinusoidal waveforms is important [6]. Fortunately, modern high-speed power switches allow the implementation of sophisticated control techniques [7] that can significantly reduce harmonics in the output voltage [8].

Multilevel inverters (MLI) provide a distinct advantage by producing staircase voltage waveforms [9] with variable magnitude and frequency [10]. It results in lower voltage stress on semiconductor devices [11] and reduced total harmonic distortion (THD) [12] in comparison to conventional inverters [13]. The increase in number of levels in a MLI provides more steps for the desired output waveform [14], thereby further minimizing harmonic distortion [15].

In a conventional cascaded H-bridge seven-level inverter [16], the architecture consists of twelve strategically arranged switches designed to prevent short circuits across the voltage sources [17]. Each voltage source provides a direct current voltage [18], allowing the inverter to achieve a maximum output

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

voltage that is three times the value of the individual source voltage [19]. The output voltage waveform consists of seven distinct levels [20]. In the positive half cycle, the voltage levels are equal to the source voltage, twice the source voltage, and three times the source voltage [21]. The waveform also includes a zero-voltage level [22]. In the negative half cycle, the voltage levels are the negative of the source voltage [23], twice the negative of the source voltage, and three times the negative of the source voltage [24].

The operation of multilevel inverters is primarily governed by control techniques [25], which can be generally divided into two main categories [26]: low switching frequency [27] and high switching frequency modulation control schemes. Sinusoidal PWM [28], a widely used high switching frequency modulation control scheme, is particularly suited for medium and high-voltage applications [29]. Among its various implementations [30], the level shifted PD (phase disposition) Sinusoidal PWM scheme provides efficient control and voltage regulation [31]. In contrast, Selective Harmonic Elimination PWM scheme is a low switching frequency modulation method designed for specific harmonic elimination, making it a preferred choice for medium and high-voltage applications where waveform quality and harmonic control are critical.

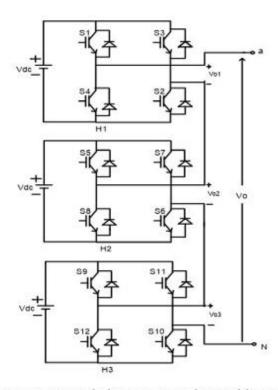

Figure 1: Cascaded Seven-Level H-Bridge Inverter

The figure 1 shows a Cascaded Seven-Level H-Bridge Inverter circuit comprising of three equal H-bridge units connected in series. Each H-bridge circuit comprises of four power semiconductor devices with feedback diodes and is driven by a separate DC voltage source. This configuration enables the generation of seven distinct voltage levels (±3Vdc, ±2Vdc, ±Vdc, 0) through appropriate switching combinations, producing a stepped waveform that approximates a sinusoidal output.

This paper presents a performance evaluation of Selective Harmonic Elimination Pulse Width Modulation (SHE-PWM) using a novel algorithm and Sinusoidal Pulse Width Modulation (SPWM) in grid-connected cascaded seven-level H-bridge inverter. The research emphases on emerging a novel optimization algorithm based on SHE-PWM to calculate optimal switching angles, focusing to minimize Total Harmonic Distortion across modulation indices from 0.7 to 1.0. The novel algorithm focuses the complexity of solving non-linear transcendental equation sets that define the relationships amongst switching angles, distortion of harmonics, and fundamental wave magnitude. Through comprehensive

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

simulation and analysis of Grid-connected cascaded 7-level H-bridge inverter, this study validates the enhanced performance attained through the implementation of the new developed optimization algorithm based on SHE, predominantly in comparison to conventional Sinusoidal PWM control scheme. The cascaded 7-level H-bridge inverter is compatible for integration with solar photovoltaic (SPV) systems.

## LITERATURE REVIEW

The literature on Selective Harmonic Elimination Pulse-width Modulation (SHE-PWM) technique for cascaded seven-level H-bridge inverters demonstrates significant advancements in harmonic mitigation strategies. Farokhnia et al. (2012) introduced an improved SHE-PWM strategy that effectively generates stepped voltage waveforms across a wide range of modulation indices, validated through simulation and experimental studies, showcasing its capability to reduce Total Harmonic Distortion (THD) significantly [32]. Moeini et al. (2014) expanded on this by developing a modified Selective Harmonic Mitigation PWM technique that employs variable DC-link voltages, meeting grid code requirements and confirming its effectiveness through both single-phase and three-phase simulations [33]. Haw et al. (2014) contributed to the field by optimizing both DC voltage levels and switching angles in their multilevel SHE-PWM approach for transformer less static synchronous compensators, enhancing harmonic elimination without altering the inverter's structure [34]. Kundu et al. (2017) performed a comparative analysis of various optimization techniques for determining precise switching angles in SHE-PWM applications, demonstrating that their proposed methods outperform traditional algorithms in terms of convergence and inverter performance [35] Lastly, Bopche et al. (2018) conducted a comparative study of modulation techniques in three-level cascaded H-bridge inverters, utilizing the Newton-Raphson method to determine optimal switching angles for effective harmonic elimination [36]. Collectively, these studies underscore the evolution and efficacy of SHE-PWM techniques in improving the performance of multilevel inverters.

# Materials and Methods Modulation Techniques Implementation

The study employed two different modulation control schemes for controlling the cascaded seven-level H-bridge inverter: Sinusoidal PWM and Selective Harmonic Elimination PWM using a novel algorithm.

# Sinusoidal PWM Implementation

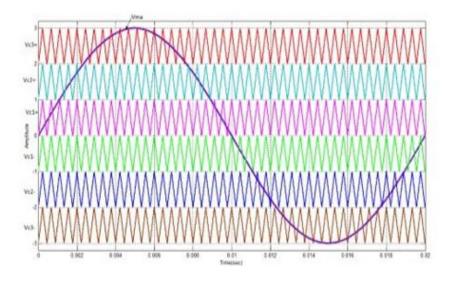

Figure 2: Sinusoidal PWM carrier and reference waveforms for a CHB 7-level inverter

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

The figure 2 shows six triangular carrier waves compared with a sinusoidal reference waveform. This arrangement implements level-shifted phase disposition PWM scheme for a CHB 7-level inverter, where the intersection points between triangular carriers and reference waveform determine the switching pulses for obtaining the staircase7-level output voltage.

The following parameters were established for the simulation: DC Bus Voltage: 100V, Carrier frequency: 2250 Hz, Fundamental frequency: 50Hz, RL Load specifications: R = 45Ohm, L = 25mH.

The implementation involved six carrier waveforms arranged with specific characteristics:

Six triangular carrier waveforms maintained the same phase. Three carriers were appeared across the positive half-cycle of the modulating signal. Three carriers were appeared across the negative half-cycle. The frequency modulation index was calculated as mf = fc/fm. The amplitude modulation index is used between  $0 \le ma \le 1$ .

# SIMULATION SETUP

Both modulation techniques, SPWM and SHE-PWM using a novel algorithm, were implemented using the MATLAB/Simulink environment. The Simulink model consisted of a complete CHB 7level inverter circuit, SPWM generator blocks, an RL load implementation, and measurement systems for voltage and current. Additionally, FFT analysis blocks were included to evaluate the harmonic content. The SHE-PWM Simulink model was designed with a modified inverter circuit incorporating optimized switching angles derived from the proposed optimization algorithm. This model implemented the calculated switching patterns and included similar measurement and analysis systems as those used in the SPWM model, ensuring consistency in performance evaluation. The comparative analysis focused on several critical metrics to evaluate the performance of both techniques. Total Harmonic Distortion (THD) was measured across modulation indices ranging from 0.7 to 1.0, using FFT analysis up to the 50th harmonic order. This allowed for a detailed comparison of harmonic performance between the two techniques. Output voltage quality was assessed through waveform analysis, fundamental voltage amplitude measurements, and an evaluation of switching patterns. Additionally, load current analysis involved assessing the quality of current waveforms, measuring current THD, and examining load response characteristics. These methods provided a comprehensive understanding of the performance differences between SPWM and SHE-PWM using a novel algorithm.

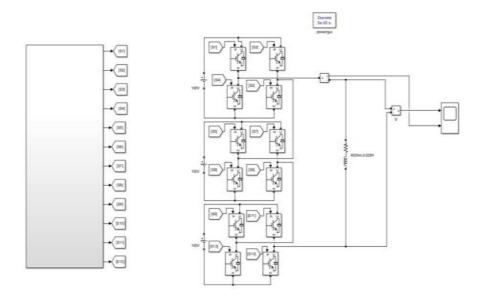

Figure 3: Simulink model of a cascaded H-bridge 7-level inverter using SPWM with RL load.

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

The figure 3 shows the complete system architecture in Simulink, consisting of a PWM signal generator, three batteries feeding separate H-bridge modules, and an RL load. Each H-bridge contains 4 IGBT switches controlled by PWM signals, with their outputs connected in series to generate the 7-level voltage waveform.

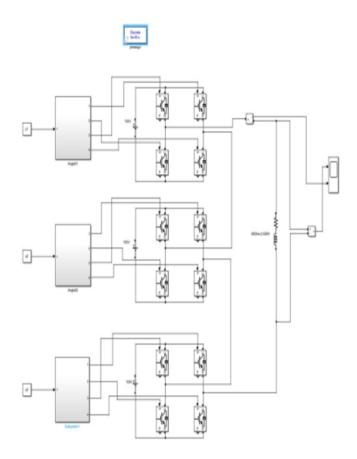

The model in figure 4 represents three series-connected H-bridge modules powered by 100V DC sources, with the output connected to an RL load (45 ohm, 0.025H). The independent control blocks (AngleG1-3) generate switching signals for each H-bridge unit to generate the desired 7-level output voltage waveform.

# Data Collection and Analysis

The study collected comprehensive data sets including:

Output voltage waveforms, Load current waveforms, THD measurements for modulation indices from 0.7 to 1.0, Harmonic spectrum analysis.

Figure 4: Simulink model of a cascaded H-bridge 7-level inverter using SHE-PWM with RL load.

The analysis methodology included:

Comparative evaluation of THD values, assessment of fundamental voltage amplitudes, analysis of harmonic spectrum distributions and performance evaluation across different modulation indices.

#### RESULTS

The comparative analysis between SHE-PWM using a novel algorithm and SPWM techniques emphasized distinguished differences in performance across various operating conditions. These differences were analyzed in several key areas, beginning with the output voltage waveform.

In the SPWM implementation, the output voltage waveform exhibited higher harmonic distortion due to the presence of significant low-order harmonics. The harmonic content was widely distributed

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

across the frequency spectrum, with characteristic high-frequency clusters further elevating the Total Harmonic Distortion (THD). This resulted in a less efficient waveform and suboptimal power quality, impacting overall system performance.

On the other hand, the SHE-PWM using a novel algorithm modulation scheme demonstrated superior output voltage characteristics. By successfully eliminating targeted low-order harmonics such as the 3rd, 5th, 7th, and 9th, SHE-PWM using a novel algorithm reduced the overall harmonic content and achieved a cleaner waveform. The remaining harmonic components were concentrated at higher frequencies, where their impact on the system's performance was minimized. This selective harmonic elimination contributed to improved THD values and better power quality across modulation indices from 0.7 to 1.0.

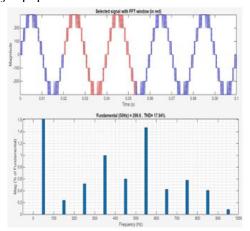

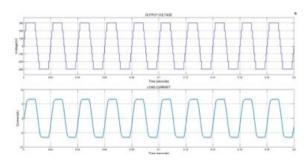

Figure 5: Output voltage and load current waveforms of a 7-level CHB inverter at modulation index Ma=1

The figure 5 upper plot shows the stepped output voltage waveform with seven distinct voltage levels (±300V, ±200V, ±100V, 0V). The figure 5 lower plot displays the corresponding sinusoidal load current waveform. The load current's smooth sinusoidal shape indicates effective harmonic reduction through multilevel switching.

The figure 6 shows the output voltage waveform with FFT analysis window highlighted in red, and its corresponding harmonic spectrum. The fundamental component at 50Hz has a magnitude of 299.6V with a THD of 17.94%. The spectrum reveals significant harmonics at multiples of the fundamental frequency, with decreasing magnitudes at higher frequencies, demonstrating the effectiveness of multilevel switching in reducing lower-order harmonics.

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

Figure 6: FFT analysis and harmonic spectrum of 7-level CHB inverter output voltage at Ma=1 using SPWM control scheme.

The output voltage waveform demonstrated clear seven-level steps The transitions between voltage levels showed characteristic high-frequency switching patterns The load current waveform exhibited smooth sinusoidal characteristics The maximum output voltage achieved was 300V (3Vdc) at Ma=1

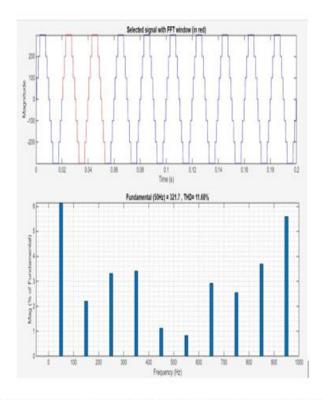

# SHE-PWM using a novel algorithm Implementation Results:

The voltage waveform maintained distinct seven-level steps with optimized switching angles transitions between levels showed reduced switching events compared to SPWM. Load current maintained sinusoidal nature with lower ripple content. The fundamental voltage component showed higher amplitude compared to SPWM. The waveforms in figure 7 demonstrates the performance of Selective Harmonic Elimination PWM (SHE-PWM) using a novel algorithm applied to a Cascaded H-Bridge 7-level inverter. The output voltage shows distinct 7-level steps (+300V, +200V, +100V, 0V, -100V, -200V, -300V) with quarter-wave symmetry. The modulation index (Ma) of 1 indicates operation at rated voltage, achieving optimal voltage utilization.

## **Total Harmonic Distortion Analysis**

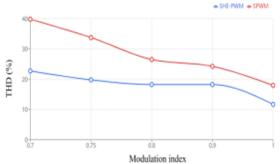

The study presented a detailed analysis of Total Harmonic Distortion (THD) across modulation indices from 0.7 to 1, highlighting the performance of Selective Harmonic Elimination Pulse Width Modulation using a novel algorithm in comparison to Sinusoidal Pulse Width Modulation. At a modulation index of 0.7, SHE-PWM achieved a THD of 22.71%, while SPWM recorded a higher THD of 26.49%, indicating a significant 3.78% reduction in THD with SHE-PWM. Similarly, at Ma = 0.75, the THD for SHE-PWM was 19.77%, compared to 24.71% for SPWM, resulting in a 4.94% improvement. For Ma = 0.8, the respective THD values were 18.22% for SHE-PWM and 24.24% for SPWM, reflecting a 6.02% reduction. At Ma = 0.9, SHE-PWM maintained a THD of 18.22%, while SPWM recorded 22.39%, showing a 4.17% improvement. Finally, at Ma = 1.0, SHE-PWM achieved a significantly lower THD of 11.68%, compared to 17.94% for SPWM, yielding a 6.26% improvement.

Figure 7: Output voltage and load current waveforms of a 7-level CHB inverter using SHE-PWM at Ma=1

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

The study also reported the outcomes of a novel optimization algorithm for determining switching angles across various modulation indices. For Ma = 0.7, the optimal switching angles were  $\theta$ 1 = 0.089573 radians,  $\theta$ 2 = 0.48406 radians, and  $\theta$ 3 = 0.26471 radians. At Ma = 1.0, the corresponding angles were  $\theta$ 1 = 0.86128 radians,  $\theta$ 2 = 0.1341 radians, and  $\theta$ 3 = 0.49674 radians. The harmonic spectrum analysis further validated the efficacy of these optimized angles in achieving enhanced performance.

The harmonic profile of SPWM exhibited characteristic high-frequency harmonic clusters, with a higher magnitude of low-order harmonics contributing to elevated distortion levels. Additionally, SPWM demonstrated a more distributed harmonic content across the spectrum, which impacts power quality negatively.

In contrast, the harmonic profile of SHE-PWM highlighted its effectiveness in eliminating targeted low-order harmonics, including the 3rd, 5th, 7th, and 9th harmonics. This selective harmonic elimination reduced the overall harmonic content significantly, resulting in a cleaner waveform. The remaining harmonic components were concentrated at higher frequencies, minimizing their impact on the system's performance and improving power quality.

These trends underscore the superior harmonic performance of SHE-PWM using a novel algorithm compared to SPWM, as it achieves better harmonic mitigation while maintaining system efficiency and waveform quality. Figure 8 demonstrates harmonic analysis of the waveform indicates a fundamental frequency component at 50 Hz with a magnitude of 321.7 V and a Total Harmonic Distortion (THD) of 11.68%. The SHE-PWM technique effectively eliminates lower-order harmonics, ensuring improved power quality. Although higher-order harmonics, particularly in the 800-900 Hz range, remain present, their magnitudes are significantly reduced, demonstrating the capability of SHE-PWM to enhance harmonic performance while maintaining system efficiency.

Figure 8: Harmonic spectrum analysis of a 7-level CHB inverter output voltage with FFT window (top) and corresponding frequency components (bottom) at Ma=1

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

Figure 9: Comparative analysis of voltage THD versus modulation index (Ma) for SHE-PWM using novel algorithm and SPWM techniques

The graph illustrates that SHE-PWM using a novel algorithm consistently outperforms SPWM in terms of THD across all modulation indices ranging from 0.7 to 1.0. As the modulation index increases, THD improves for both techniques, with SHE-PWM achieving its best performance at Ma = 1.0, where the THD is reduced to 11.68%. In contrast, SPWM exhibits higher distortion throughout the modulation range, highlighting the superior harmonic performance of SHE-PWM.

In terms of the fundamental voltage component, SHE-PWM demonstrated a higher amplitude and better voltage utilization compared to SPWM. Additionally, SHE-PWM maintained a more stable fundamental component across the modulation range.

Regarding switching characteristics, SPWM showed higher switching frequency operation, while SHE-PWM achieved reduced switching events, resulting in lower switching losses. These advantages make SHE-PWM more efficient in terms of energy consumption and thermal management.

The load current quality produced by both techniques was acceptable; however, SHE-PWM slightly surpassed SPWM by delivering better current quality and reduced current ripple. This improvement in current waveform quality further validates the effectiveness of the SHE-PWM technique.

The results clearly demonstrate the superiority of the SHE-PWM technique, especially when combined with the new optimization algorithm, over the conventional SPWM approach. Significant improvements were observed in reducing THD across all modulation indices, better fundamental voltage utilization, successful elimination of targeted low-order harmonics, reduced switching losses due to lower switching frequency, and enhanced overall waveform quality. These findings underscore the effectiveness of the proposed optimization algorithm and highlight the advantages of SHE-PWM for cascaded H-bridge multilevel inverter applications.

# **DISCUSSION**

The comparative analysis of selective harmonic elimination pulse width modulation using a novel algorithm and sinusoidal pulse width modulation for the cascaded seven-level H-bridge inverter reveals several important insights into their performance characteristics. The most notable result is the consistent superiority of selective harmonic elimination in reducing total harmonic distortion across all modulation indices, with improvements ranging up to 6.26 percent for sinusoidal pulse width modulation.

The reduction in total harmonic distortion achieved by selective harmonic elimination can be attributed to two key factors. First, the method successfully eliminates specific low-order harmonics, namely the third, fifth, seventh, and ninth harmonics, by using optimized switching angles. This significantly improves the quality of the output waveform. Second, the new optimization algorithm effectively determines the optimal switching angles required to minimize the overall harmonic content while preserving the desired fundamental voltage component. An interesting observation is the inverse relationship between modulation index and total harmonic distortion for both techniques. At a

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

modulation index of one, both methods yield their lowest total harmonic distortion values, with selective harmonic elimination achieving 11.68 percent and sinusoidal pulse width modulation achieving 17.94 percent. However, the performance gap between the two techniques widens at lower modulation indices, with selective harmonic elimination maintaining better distortion characteristics.

There is also a clear trade-off between switching frequency and harmonic performance. Sinusoidal pulse width modulation operates at higher switching frequencies, which can lead to increased switching losses, while selective harmonic elimination achieves superior harmonic performance with fewer switching events. This makes selective harmonic elimination particularly attractive for high-power applications where minimizing switching losses is critical.

These findings have significant practical implications. The superior total harmonic distortion performance and reduced switching losses of selective harmonic elimination make it especially suitable for high-power applications where waveform quality and efficiency are paramount. However, the increased implementation complexity of selective harmonic elimination, due to the need for sophisticated optimization algorithms, should be weighed against the simpler implementation of sinusoidal pulse width modulation in applications where moderate harmonic performance is acceptable.

Future research may focus on extending the optimization algorithm to accommodate higher-level inverters and on investigating the impact of non-ideal conditions, such as voltage imbalances and device mismatches, on the performance of both modulation techniques.

# **CONCLUSION**

This study presents a comprehensive comparative analysis between Selective Harmonic Elimination Pulse Width Modulation using a new optimization algorithm and Sinusoidal Pulse Width Modulation for controlling cascaded H-bridge seven-level inverters. The results clearly demonstrate that the Selective Harmonic Elimination technique, when implemented with the proposed optimization algorithm, consistently outperforms the Sinusoidal PWM technique across all modulation indices ranging from 0.7 to 1.0. The key findings indicate that the Selective Harmonic Elimination method achieves significantly lower Total Harmonic Distortion than the Sinusoidal method, with distortion values reduced by up to 6.26 percent at higher modulation indices and maintaining superior performance at higher modulation indices. For instance, at a modulation index of one, the Selective Harmonic Elimination technique achieves a Total Harmonic Distortion of 11.68 percent compared to 17.94 percent for the Sinusoidal approach. The new optimization algorithm successfully generates optimal switching angles that effectively eliminate targeted low-order harmonics while preserving the desired fundamental voltage component. Furthermore, the lower switching frequency operation of the Selective Harmonic Elimination technique results in reduced switching losses, making it particularly suitable for high-power applications. Overall, these results validate the effectiveness of the proposed optimization algorithm and establish the Selective Harmonic Elimination method as the preferred modulation technique for cascaded H-bridge multilevel inverters in applications where waveform quality and efficiency are of paramount importance.

# **DECLARATIONS**

**Authors' Contributions:** S. Anasane performed the literature review, experiments, and code development. R. Tirole conceptualized the study and assisted in data analysis. All authors contributed to the development of visualizations and interpretation of results. S. Anasane prepared the original manuscript draft, and A. Bhaskar, A. Ghosh, R. Tirole reviewed and edited the manuscript. All authors reviewed and approved the final manuscript.

**Competing Interests:** The authors declare no competing interests.

Funding: This research was conducted without any external funding support.

Conflicts of Interest: The authors declare no conflicts of interest.

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php

Availability of Data and Material: Data and materials associated with this study will be provided upon reasonable request to the corresponding author.

**Code Availability:** The code developed for this study will be shared upon reasonable request to the authors. **Ethics Approval:** All experimental protocols were reviewed and approved by the institutional ethical committee. **Consent to Participate:** Informed consent was obtained from all participants involved in this study.

**Consent for Publication:** All necessary permissions for publication were obtained from participants as required.

#### **Ethics Declarations:**

- 1) The work is entirely original and has not been published previously.

- 2) It is not under consideration for publication elsewhere.

- 3) The research findings and analysis are truthful and complete.

- 4) All contributors have been properly acknowledged.

- 5) The results have been contextualized within the relevant body of research.

## **REFERENCES**

- [1] Amarjit Roy, Chiranjit Sain, Raja Ram Kumar et al. Intelligent Computation and Analytics on Sustainable Energy and Environment. 2024.

- [2] Subhashree Choudhury, Mohit Bajaj, Taraprasanna Dash, Salah Kamel and Francisco Jurado. "Multilevel inverter: A survey on classical and advanced topologies, control schemes, applications to power system and future prospects". *Energies*, vol. 14, no. 18, 5773, 2021.

- [3] Roberta Di Fonso. "Batterie multilivello per la mobilità elettrica e le smart grid: dai modelli di cella al comportamento di sistema". 2023.

- [4] Shoaib Munawar, Muhammad Sajid Iqbal, Muhammad Adnan, Muhammad Ali Akbar and Amine Bermak. "Multilevel Inverters Design, Topologies, and Applications: Research Issues, Current, and Future Directions". *IEEE Access*, 2024.

- [5] Ali Bughneda, Mohamed Salem, Anna Richelli, Dahaman Ishak and Salah Alatai. "Review of multilevel inverters for PV energy system applications". *Energies*, vol. 14, no. 6, 1585, 2021.

- [6] Nidhal Kamel Taha El-Omari, Ahmad H Al-Omari, Ali Mohammad H Al-Ibrahim and Tariq Alwada'n. "Inter- national Journal of Basic Sciences and Applied Computing (IJBSAC) International Journal of Basic Sciences and Applied Computing (IJBSAC)".

- [7] FEIGUO JIANG and Q I TU. Advanced Voltage Quality Controller for New Power Distribution Systems. Springer, 2025.

- [8] Tibin Joseph, Carlos E Ugalde-Loo, Jun Liang and Paul F Coventry. "Asset management strategies for power electronic converters in transmission networks: Application to HVDC and FACTS devices". *IEEE access*, vol. 6, 21084–21102, 2018.

- [9] Jun Yin Lee, Renuga Verayiah, Kam Hoe Ong, Agileswari K Ramasamy and Marayati Binti Marsadek. "Dis-tributed Generation: A review on current energy status, grid-interconnected PQ issues, and implementation constraints of DG in Malaysia". *Energies*, vol. 13, no. 24, 6479, 2020.

- [10] W Abd Halim, S Ganeson, M Azri and TNA Tengku Azam. "Review of multilevel inverter topologies and its applications". *Journal of Telecommunication, Electronic and Computer Engineering (JTEC)*, vol. 8, no. 7, 51–56, 2016.

- [11] Mihai Ciobotaru, Florin Iov, Pericle Zanchetta and Steffano Biffarette. "Advanced power

ISSN: 2229-7359 Vol. 11 No. 6s, 2025

https://www.theaspd.com/ijes.php converters for universal and flexible power management in future electricity network-Report on Control Strategies". 2008.

- [12] O Bay, M T Tran, M El Baghdadi, S Chakraborty and O Hegazy. "A Comprehensive Review of GaN-Based Bi-Directional On-Board Charger Topologies and Modulation Methods. Energies 2023, 16, 3433", 2023.

- [13] Vijayakumar Arun, Albert Alexander Stonier, Geno Peter, K Ezhil Vignesh and D Ferlin Deva Shahila. "9- Level switched capacitor-high-voltage gain boosting inverter (SC-HVGBI) topology with reduced voltage stress". *Electrical Engineering*, pages 1–17, 2024.

- [14] Thomas Strasser, Filip Andrén, Johannes Kathan et al. "A review of architectures and concepts for intelligence in future electric energy systems". *IEEE Transactions on Industrial Electronics*, vol. 62, no. 4, 2424–2438, 2014.

- [15] Prabhat Ranjan Bana, Kaibalya Prasad Panda, R T Naayagi, Pierluigi Siano and Gayadhar Panda. "Recently developed reduced switch multilevel inverter for renewable energy integration and drives application: topolo- gies, comprehensive analysis and comparative evaluation". *IEEE access*, vol. 7, 54888–54909, 2019.

- [16] Shravana Kumar Musunuri. "Control and interface design for cost reduction of a low power grid-connected wind-photovoltaic system". 2011.

- [17] Mohamed Riadh Ouargli and Imad Eddine Boukerche. "Fault detection and prognosis for multilevel inverter".

- [18] Olcay Bay, Manh Tuan Tran, Mohamed El Baghdadi, Sajib Chakraborty and Omar Hegazy. "A comprehensive review of gan-based bi-directional on-board charger topologies and modulation methods". *Energies*, vol. 16, no. 8, 3433, 2023.

- [19] Yohannes Israel, Assaad Maher and Hamid Nor Hisham. "A CMOS Interface Circuit Design for a 32-level Resolution Light Sensor". 2013.

- [20] S Granata, M Di Benedetto, C Terlizzi et al. "Power Electronics Converters for the Internet of Energy: A Review. Energies 2022, 15, 2604", 2022.

- [21] Nishalini Delcy Arokianathan, Francis Thomas Josh, Evelyn Brindha et al. "Bi-directional DC-AC using BLDC motor for electric and hybrid electric vehicles applications with reduced number of switches". International Journal of Power Electronics and Drive Systems (IJPEDS), vol. 15, no. 2, 1081–1090, 2024.

- [22] M Malarvizhi, R Nagarajan, M Meenakshi and R Banupriya. "Unipolar Sine Multicarrier SPWM Control Strategies for Seven-Level Cascaded Inverter". *International Journal of Emerging Technologies in Engineer- ing Research (IJETER)*, vol. 6, no. 1, 111–117, 2018.

- [23] Muhammad Waqas. "Design and analysis of a hybrid power system for remote natural gas pipeline control stations", 2024.

- [24] H Aboub, R Mechouma, C Labiod and A Khechekhouche. "A New Multicarrier Sinusoidal Pulse Width Mod- ulation (SPWM) Strategy based on Rooted Tree Optimization (RTO) Algorithm for Reducing Total Harmonic Distortion (THD) of Switched-Capacitor Nine-level Inverter in Grid-connected PV systems". *Indonesian Journal of Science and Technology*, vol. 7, no. 1, 19–36, 2022.

- [25] Dominik Neumayr, Dominik Bortis and Johann Walter Kolar. "The essence of the little box challenge-part A: Key design challenges & Samp; solutions". CPSS Transactions on Power Electronics and Applications, vol. 5, no. 2, 158–179, 2020.